Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:08.

- Zadnja izmjena 2025-01-23 14:37.

Ovo je vodič o tome kako izgraditi štopericu od jedne minute pomoću VHDL -a i Basys 3 ploče. Takav uređaj idealan je za igre u kojima svaki igrač ima najviše jednu minutu za svoj potez. Štoperica precizno prikazuje sekunde i milisekunde na ekranu sa sedam segmenata, počevši od 0 sekundi i 0 milisekundi, do 60 sekundi i 0 milisekundi. Koriste se i dva dugmeta: centralno dugme, koje se koristi za pokretanje, zaustavljanje i nastavak mjerača vremena, te desno dugme za ponovno pokretanje mjerača vremena. Kada se uređaj uporedi uporedo sa ugrađenom štopericom pametnog telefona, tačnost sata je primjetna.

Korak 1: Nabavite hardver/softver

1. Basys 3 Artix-7 FPGA trenažerna ploča od Digilenta s mikro USB-om do USB kabela

2. Vivado 2016.2 Design Suite iz Xilinxa

Korak 2: Blok dijagram

Ovo kolo je konstruisano bihevioralno i koristi ugrađene Xilinx komponente, ali se može i strukturno opisati, kao što je prikazano gornjim općim strukturnim dijagramom. Iz dijagrama se može vidjeti da krug pokreću dva razdjelnika frekvencije. Jedan od razdjelnika frekvencije radi na 1 centisekundi i pokreće katodni brojač koji se koristi kao brojevi prikazani na ekranu sa sedam segmenata. Drugi djelitelj frekvencije radi na 240Hz i koristi se za pokretanje brojača anode koji se rotira kroz anode tako da se svi brojevi pravilno prikazuju na ekranu sa sedam segmenata. Enkoder uzima katodnu logiku iz katodnog brojača i anodnu logiku iz anodnog brojača i kodira je na izlaznu katodu i anodu koja pokreće sedmosegmentni prikaz. Funkcija ovog kodera je da se izlaz katode mijenja svaki put kada se promijeni izlaz anode. Izlaz katode ne može se pokrenuti nezavisno od brojača jer se anode moraju rotirati kroz 4 zasebne znamenke.

Korak 3: Modul projekta

Prvo, procesni blok za CEN je napravljen tako da kada se otkrije pritisak na tipku, ENABLE će se prebaciti. Ovo služi kao zaustavljanje/pokretanje katodnog brojača.

U sljedećem procesnom bloku signali takta centisekunde i 240Hz postavljeni su tako da se njihovi brojači povećavaju za 1 svaki put kada interni sat od 100 mHz dosegne rastuću ivicu. Kad brojač u centisekundi dosegne 500000, vratit će se na 0. U međuvremenu će se brojač od 240 Hz resetirati kada broj dostigne 41667.

Za dio katode koda, ako je ENABLE '0', brojanje katoda će se pauzirati. Ako se pritisne tipka za poništavanje tijekom tog vremena, tada se svi brojevi vraćaju na "0000". U međuvremenu, ako je ENABLE "1", katodno brojanje će se nastaviti sve dok katodni broj ne dosegne 60,00, pri čemu se aktivira signal za zaustavljanje na "1". Zaustavni signal se vraća natrag u procesni blok CEN i uzrokuje da ENABLE bude '0', dok je signal za zaustavljanje '1' i neće se promijeniti sve dok se ne pritisne tipka za resetiranje.

Konačno, zaslon sa sedam segmenata postavljen je tako da su 4 anode pravilno spojene sa svakom od svojih 8 katoda kako bi prikazale svoje odgovarajuće znamenke 0-9 istovremeno.

Korak 4: Ograničenja

Ova datoteka ograničenja povezuje navedene ulaze i izlaze iz VHDL -a u potrebne, fizičke dijelove Basys ploče. Za ovaj projekt, komponente uključuju četiri anode i svaku od svojih osam katoda za sedmo segmentni prikaz, interni sat od 100 mHz, središnje dugme i desno dugme.

Korak 5: Testirajte

Nakon što dovršite kôd, sada možete programirati FPGA putem USB kabela. Prikaz sa sedam segmenata trebao bi pokazati 0.00. Testirajte da li tipke rade pritiskom na centralno dugme za pokretanje mjerača vremena dok ne dosegne 60,00 i zaustavi se; u bilo koje vrijeme možete ponovo pritisnuti centralno dugme da biste ga pauzirali. Nakon što je pauziran, možete pritisnuti desno dugme da biste vratili mjerač vremena na 0,00. Ako sve radi ispravno, čestitamo što ste upravo izgradili tajmer za jednu minutu!

Preporučuje se:

Štoperica Arduino Leonardo: 3 koraka

Arduino Leonardo štoperica: Kredit: https://www.instructables.com/id/Arduino-Stopwatch…Ova izvedba štoperice potječe iz gornje veze, štoperice koja broji od 1, dok ova odbrojava od 60 sekundi . Većina koda koji sam koristio slijedi original

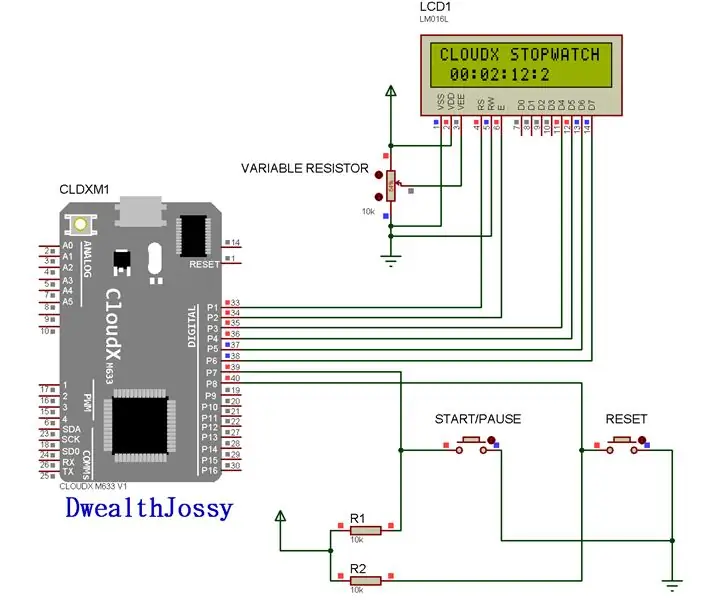

Jednostavna CloudX M633 digitalna štoperica: 4 koraka

Jednostavna CloudX M633 digitalna štoperica: U ovom projektu napravit ćemo verziju digitalnog sata koji može bilježiti sate, minute i sekunde, poput štoperice na vašem mobilnom telefonu! Koristit ćemo LCD za prikaz vremena

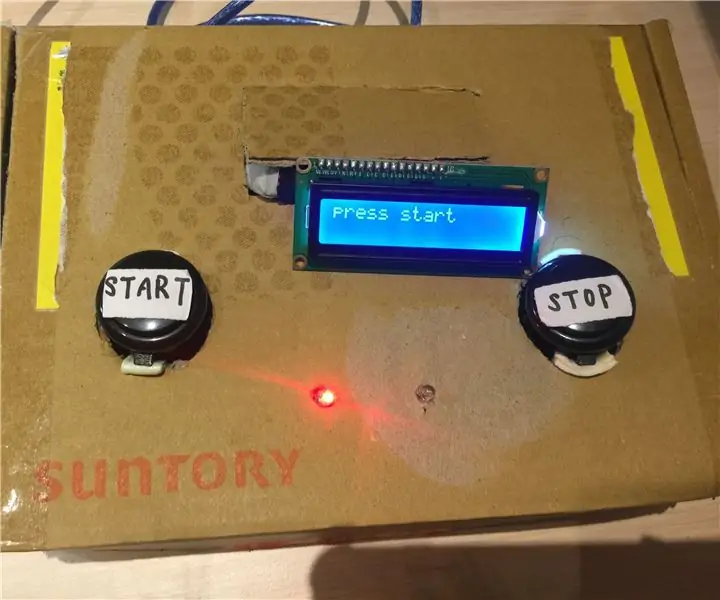

Arduino projekt - štoperica: 3 koraka

Arduino projekt - Štoperica: Ova štoperica može se upotrijebiti za mjerenje vremena koje želite, na primjer, vrijeme potrebno za završetak zadatka ili za stvaranje pritiska na vrijeme koje je potrebno za završetak posla. LED diode pomažu korisniku da jasno zna vrijeme početka i zaustavljanja. Ovaj projektni izvor

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: 9 koraka

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: Dobro došli u uputstva o tome kako izgraditi štopericu koristeći osnovnu VHDL i Basys 3 ploču. Sa zadovoljstvom dijelimo naš projekt s vama! Ovo je bio završni projekt za kurs CPE 133 (digitalni dizajn) na Cal Polyu, SLO u jesen 2016. Projekt koji smo izgradili

VHDL štoperica: 8 koraka (sa slikama)

VHDL štoperica: Ovo je vodič o tome kako napraviti štopericu pomoću VHDL-a i FPGA ploče, poput Basys3 Atrix-7 ploče. Štoperica može brojati od 00,00 sekundi do 99,99 sekundi. Koristi dva dugmeta, jedno za dugme start/stop, a drugo za dugme