Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:05.

- Zadnja izmjena 2025-01-23 14:37.

Autor AmCoderhttps://www.linkedin.com/in/mituFollow Više od autora:

O: Mitu Raj - samo hobist i učenik - Dizajner čipova - Programer softvera - Ljubitelj fizike i matematike Više o AmCoderu »

## Ovo je najpopularnija, najpopularnija veza u Googleu za VHDL implementaciju CORDIC ALGORITHM -a za generiranje sinusnog i kosinusnog vala ## Trenutno postoje mnogi hardverski efikasni algoritmi, ali oni nisu dobro poznati zbog dominacije softverskih sistema nad mnogo godina. CORDIC je takav algoritam koji nije ništa drugo do skup logika pomaka i dodavanja koji se koriste za računanje širokog raspona funkcija uključujući određene trigonometrijske, hiperboličke, linearne i logaritamske funkcije. Ovo je algoritam koji se koristi u kalkulatorima itd. Dakle, samo pomoću jednostavnih mjenjača i sabirača možemo dizajnirati hardver manje složenosti, ali snage DSP -a koristeći kordični algoritam. Stoga se može dizajnirati kao goli RTL dizajn u VHDL -u ili Verilogu bez upotrebe namjenskih jedinica s pomičnim zarezom ili složenih matematičkih IP adresa.

Korak 1: VHDL i Modelsim

Ovdje je kordirani algoritam implementiran pomoću VHDL -a za generiranje sinusnog i kosinskog vala. Može prikazati sinus i kosinus ulaznog ugla sa velikom preciznošću. Kod se može sintetizirati na FPGA. Modelsim se koristi za simulaciju dizajna i ispitnog stola.

Korak 2: VHDL kôd za dizajn i ispitnu klupu

Binarna tehnika skaliranja koristi se za predstavljanje brojeva s pomičnim zarezom.

Prije kodiranja, prođite kroz priložene dokumente.

Prođite kroz stimulaciju cordic_v4.vhd - Dizajn - Ulaz je kut u 32 bita + predznak; može obraditi bilo koji ugao od 0 do +/- 360 stepeni sa preciznošću unosa od 0,000000000233 stepena. Pri davanju ulaza -> MSB je predznak, a ostalih 32 bita predstavljaju veličinu. -Izlaz dizajna je njegov sinus i cos vrijednost u 16 bita + predznak.ie; sa preciznošću 0,00001526. Imajte na umu da je izlaz prikazan u obliku komplimenta 2 ako je odgovarajuća sinusna ili cos vrijednost negativna. Simulacija testb.vhd - Testna ploča za dizajn (1) Ulazni kutovi i povlačenje povlačenjem = '0'. Nakon dva koraka simulacije povucite resetiranje na '1' i "pokreni sve". (2) U prozoru simulacije postavite radiks sin i cos signala kao decimalni i format> Analogni (automatski). (3) Umanjite prikaz da biste vidjeli valni oblik pravilno.

Korak 3: Priložene datoteke

(1) cordic_v4.vhd - Dizajn. (2) testb.vhd - Testni sto za projektovanje.

(3) Dokument o tome kako forsirati kutne unose i pretvoriti binarne rezultate.

Ažuriranje: OVI DATOTEKE NISU VEZDANI I NE DOSTAVLJAJU SE VIŠE. MOLIMO KORISTITE DATOTEKE IZ SLJEDEĆEG KORAKA

Korak 4: Mini -Cordic IP jezgro - 16 bita

Ograničenje gore navedene implementacije je spora, niža radna frekvencija zbog računanja u jednom ciklusu takta. Mini-Cordic IP Core- 16 Bit

- Kritične staze raspoređene na više ciklusa radi poboljšanja performansi.- Brže- FPGA provjereni dizajn sintetiziran do takta od 100 Mhz.- Više područja optimizirano u HDL-u, Manji hardver.- Dodani su signali učitavanja i gotovog stanja.- Jedina mana je manja rezolucija u odnosu na prethodni. Testbench:

potpuno automatizirani od 0 do 360 stupnjeva

Priložene datoteke: 1) mini kabelska glavna vhdl datoteka2) mini kabelska ispitna klupa3) Mini Cordic IP Core priručnik4) Doc o tome kako forsirati kutove i pretvoriti rezultate

Za sve upite, slobodno me kontaktirajte:

Mitu Raj

pratite me:

mail: iammituraj@gmail.com

### Ukupno preuzimanja: 325 do 01.05.2021 ###

### Zadnja izmjena koda: jul-07-2020 ###

Preporučuje se:

Samobalansirajući robot - PID kontrolni algoritam: 3 koraka

Samobalansirajući robot - PID kontrolni algoritam: Ovaj projekt je zamišljen jer sam bio zainteresiran za saznanje više o kontrolnim algoritmima i kako učinkovito implementirati funkcionalne PID petlje. Projekt je još uvijek u fazi razvoja jer Bluetooth modul tek treba biti dodat, što će omogućiti

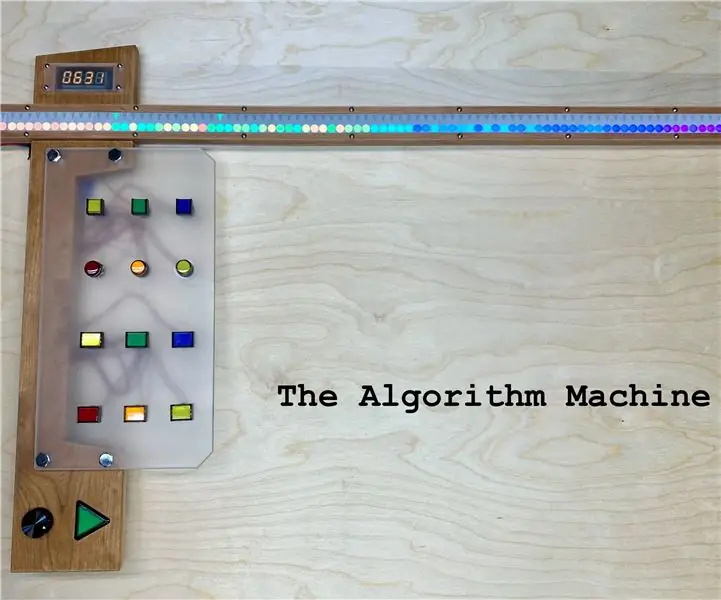

Mašina za algoritam: 13 koraka (sa slikama)

Mašina za algoritam: Predajem informatiku na fakultetu 15 godina, i iako je moja stručnost više vezana za programiranje, i dalje provodim dosta vremena pokrivajući standardne algoritme za pretraživanje i sortiranje. Sa nastavnog stanovišta

Umjetna inteligencija za društvene igre: minimalni algoritam: 8 koraka

Umjetna inteligencija za društvene igre: Minimaksni algoritam: Jeste li se ikada zapitali kako nastaju računari protiv kojih igrate šah ili dame? Pa ne tražite dalje od ovog Instructable -a jer će vam pokazati kako napraviti jednostavnu, ali efikasnu umjetnu inteligenciju (AI) koristeći Minimax Algoritam! Korišćenjem

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: 9 koraka

Osnovna štoperica pomoću VHDL -a i Basys3 ploče: Dobro došli u uputstva o tome kako izgraditi štopericu koristeći osnovnu VHDL i Basys 3 ploču. Sa zadovoljstvom dijelimo naš projekt s vama! Ovo je bio završni projekt za kurs CPE 133 (digitalni dizajn) na Cal Polyu, SLO u jesen 2016. Projekt koji smo izgradili

Tic Tac Toe na Arduinu sa AI (minimalni algoritam): 3 koraka

Tic Tac Toe na Arduinu sa AI (Minimax Algoritam): U ovom Instructable -u ću vam pokazati kako izgraditi Tic Tac Toe igru sa AI -om koristeći Arduino. Možete igrati protiv Arduina ili gledati Arduino kako igra protiv sebe. Koristim algoritam zvan "minimaksni algoritam"