Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:06.

- Zadnja izmjena 2025-01-23 14:37.

Prezadovoljna sam odgovorima koje dobijem na ovom blogu. Hvala momci što ste posjetili moj blog i motivirali me da podijelim svoje znanje s vama. Ovaj put ću vam predstaviti dizajn još jednog zanimljivog modula koji vidimo u svim SOC -ovima - Interrupt Controller.

Dizajnirat ćemo jednostavan, ali moćan programabilni kontroler prekida. To je potpuno konfigurabilan i parametriziran dizajn koji je prenosiv na različite platforme. Dizajnirao sam ovo nakon što sam puno čitao o nekim popularnim arhitekturama kontrolera prekida kao što su NVIC, 8259a, RISC-V PLIC, Microblaze's INTC itd. Nadam se da će vam ovaj blog biti od pomoći i pomoći vam da osjetite kako procesor rješava prekide uz pomoć kontrolera prekida.

Korak 1: Specifikacije

Slijede specifikacije IP -a:

- AHB3-Lite interfejs.

-

Statistički podesivi parametri:

- Broj spoljnih izvora prekida; podržava do 63 prekida.

- Br. Nivoa prioriteta; podržava do 63 nivoa.

- Broj nivoa gniježđenja; podržava do 8 nivoa gniježđenja.

- Širina sabirnice; 32 ili 64.

- Globalno i lokalno maskirani prekidi.

- Dinamički konfiguriran nivo prioriteta za svaki prekid.

- Dva načina rada - potpuno ugniježđen način rada i način jednakog prioriteta.

- Podržava osjetljive prekide aktivnog i visokog nivoa.

U dizajnu se koristi mehanizam za rukovanje prekidanjem rukovanja inspiriran specifikacijama RISC-V PLIC.

Prevencija prekida je inspirirana 8259a

Ostalo glasi: Microblaze INTC, NVIC

Korak 2: Pregled PIC -a

Programabilni kontroler prekida (PIC) prima više prekida sa vanjske periferije i spaja ih u jedan izlaz prekida sa jezgrom ciljnog procesora.

PIC se kontrolira putem kontrolnih i statusnih registara. Svi PIC registri su preslikani u memoriju i pristupa im se preko sučelja sabirnice AHB3-Lite.

Banka registara sastoji se od registra konfiguracije, registara za omogućavanje, registara na čekanju, registara u službi, registara prioriteta i registra identifikatora, koji su tipični za kontrolere prekida.

Konfiguracijski registar se koristi za postavljanje načina rada PIC -a. Može raditi u potpuno ugniježđenom načinu rada ili u režimu jednakog prioriteta.

Svakom prekidu se mogu dodijeliti prioriteti i pojedinačno maskirati. Globalno maskiranje svih prekida je također podržano.

Banka registara stupa u interakciju s prioritetnim rješavačem i BTC-om (Binary-Tree-Comparator) radi rješavanja prioriteta čekajućih prekida i u skladu s tim potvrđuje prekid procesoru. Registar ID -ova sadrži ID najvišeg prioriteta koji čeka na prekid.

Korak 3: Dizajn i implementacija RTL -a

PIC -ov dizajn naglasak stavlja na smanjenje kašnjenja u rješavanju prioriteta, što je dio vremena koji je najvažniji dio dizajna. Budući da dizajn rješava prioritete u jednom ciklusu takta, performanse se smanjuju povećanjem broja izvora sa Log2 složenošću.

Dizajn je uspješno proveden i provjereno vrijeme do sljedećih frekvencija na Artix-7 FPGA-ovima.

- Do 15 izvora: 100 MHz

- Do 63 izvora: 50 MHz

Latencija prekida dodana samo od strane PIC -a je 3 takta (isključujući vrijeme prebacivanja konteksta procesora i vrijeme dohvaćanja prve ISR instrukcije).

Korak 4: Važne napomene i priložene datoteke

Važne napomene:

- Ako je sučelje AHB3-Lite neželjeno, možete promijeniti gornji modul i upotrijebiti skeletni dizajn PIC-a. Međutim, predviđena ispitna ploča namijenjena je IP-u s AHB3-Lite sučeljem.

- PIC IP v1.0 je potpuno prenosiv, goli RTL dizajn.

- Funkcionalno provjereno radi na oba načina rada.

Priložene datoteke:

- Dizajn kodovi i ispitni sto u VHDL -u.

- Potpuna IP dokumentacija.

To je dizajn otvorenog koda … Slobodno koristite …

Za bilo koje upite, u bilo koje vrijeme:

Mitu Raj

Preporučuje se:

Laboratorija prekida (rad u toku): 3 koraka

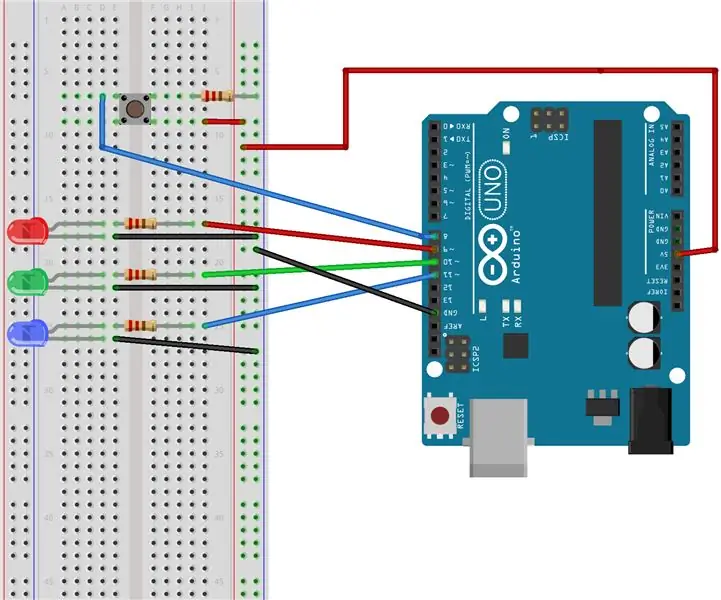

Laboratorija prekida (rad u tijeku): Svrha ove laboratorije je pokretanje Arduino programa pomoću prekida. Ova laboratorija ne radi u potpunosti ispravno zbog problema s kodiranjem. Ono što će vam trebati:- 1 Arduino Uno- 1 Breadboard- 1 tipka- 3 LED-a- otpornici od 220 ohma- kratkospojne žice

Dizajn jednostavnog četvorosmjernog asocijativnog kontrolera predmemorije u VHDL-u: 4 koraka

Dizajn jednostavnog četvorosmjernog asocijativnog kontrolera predmemorije u VHDL-u: U mojim prethodnim uputama vidjeli smo kako dizajnirati jednostavan kontroler predmemorije s direktnim mapiranjem. Ovaj put idemo korak dalje. Dizajnirat ćemo jednostavan četverosmjerni set asocijativnih kontrolera predmemorije. Prednost? Manje propuštanja, ali po cijenu performanse

Dizajn jednostavnog kontrolera predmemorije u VHDL -u: 4 koraka

Dizajn jednostavnog kontrolera predmemorije u VHDL -u: Pišem ovo uputstvo, jer mi je bilo malo teško nabaviti neki referentni VHDL kôd za učenje i započeti dizajniranje kontrolera predmemorije. Stoga sam sam dizajnirao predmemorijski kontroler od nule i uspješno ga testirao na FPGA. Imam p

Dizajn jednostavnog VGA kontrolera u VHDL -u i Verilogu: 5 koraka

Dizajn jednostavnog VGA kontrolera u VHDL -u i Verilogu: U ovom uputstvu ćemo dizajnirati jednostavan VGA kontroler u RTL -u. VGA kontroler je digitalno kolo dizajnirano za pogon VGA ekrana. Čita iz Frame Buffer -a (VGA memorija) koji predstavlja okvir za prikaz i generira potrebno

AVR mikrokontroler. LED treperi pomoću tajmera. Tajmeri prekida. Tajmer CTC način rada: 6 koraka

AVR mikrokontroler. LED treperi pomoću tajmera. Tajmeri prekida. Tajmer CTC način rada: Pozdrav svima! Tajmeri su važan koncept u oblasti elektronike. Svaka elektronička komponenta radi na vremenskoj osnovi. Ova vremenska baza pomaže da se sav rad uskladi. Svi mikrokontroleri rade na unaprijed definiranoj taktnoj frekvenciji