Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:05.

- Zadnja izmjena 2025-01-23 14:37.

Ovim štitom povežite svoju razvojnu ploču Mojo na vanjske ulaze.

Šta je Mojo razvojna ploča?

Mojo razvojna ploča je razvojna ploča zasnovana na Xilinx spartan 3 FPGA. Ploču je izradio Alchitry. FPGA su vrlo korisne u slučajevima kada se više procesa mora izvesti istovremeno.

Šta će vam trebati?

Supplies

Mojo razvojna ploča

Gerberova datoteka

8 x 15k ohm otpornici (opcionalno*)

4 x 470 ohmski otpornici

4 x 560 ohm otpornici

4 x CC 7 -segmentnih ekrana

4 x 3 mm LED diode

4 x SPDT taktilni prekidači

1 x 4 -položajni DIP prekidač za površinsko montiranje

2 x 25 sa 2 ili 4 x 25 zaglavlja

1x glava kutije 2x2 sa 5 pinova

Lemilica

Solder

Tok

*(ako su ovi otpornici izostavljeni, unutrašnje povlačenje/povlačenje mora biti omogućeno za odgovarajuće pinove)

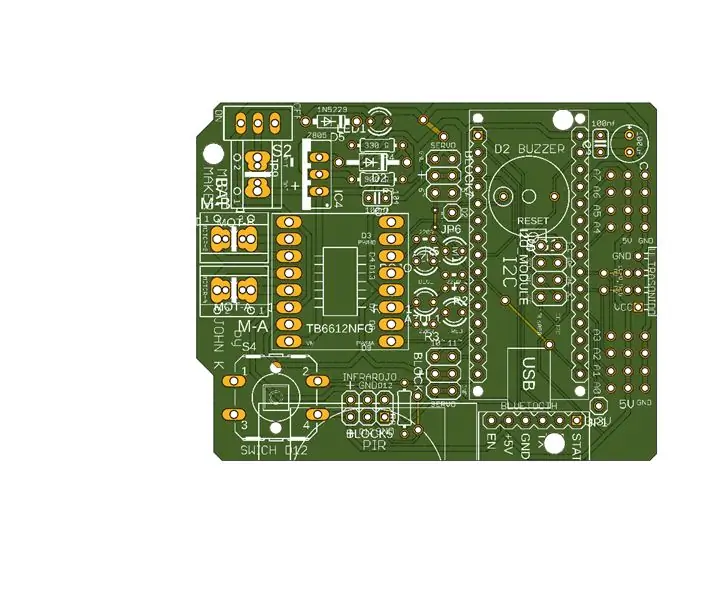

Korak 1: Pošaljite Gerber na proizvođača PCB -a po vašem izboru

Za svoje ploče naručio sam od JLC PCB -a.

Jedina promjena koju sam napravio je boja koju sam želio uskladiti sa crnom boje Mojoa.

Korak 2: Skupština odbora

Prilikom lemljenja uvijek mi je korisno lemiti najniže dijelove pa je dobra ideja započeti s otpornicima.

R5, R6, R7, R8, R9, R10, R11 i R12 su 15k ohmski otpornici koji se koriste za povlačenje prekidača (ako koristite interno povlačenje/povlačenje zanemarite ovo).

R1, R2, R3, R4 su otpornici od 560 ohma koji su odgovorni za ograničavanje struje kroz 7 -segmentni zaslon.

R13, R14, R15, R16 su otpornici od 470 ohma koji su odgovorni za ograničavanje struje kroz 4 LED diode.

Zatim lemite dip prekidač, taktilne prekidače, LED diode, sedam segmentnih ekrana i konektor zaglavlja kutije tim redoslijedom.

Sada postavite 25 na 2 (ili 2 25 na 1) u mojo kako biste poravnali pinove. Poravnajte štit s iglama i lemite ga na mjesto.

Korak 3: Postavljanje softvera

Za softver koji se odnosi na web stranicu Alchitry reći će vam šta vam je potrebno za početak i instaliranje Xilinx ISE -a. Međutim, promijenite.ucf datoteku tako da zna koji su pinovi povezani sa onim što je važno za pokretanje vašeg programa.

Evo.ucf datoteke koju koristim sa štitom:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz VISOKO 50%; NETO "clk" LOC = P56 | IOSTANDARD = LVTTL; NETO "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NETO "cclk" LOC = P70 | IOSTANDARD = LVTTL; NETO "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NETO "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NETO "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NETO "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NETO "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NETO "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NETO "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NETO "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NETO "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NETO "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NETO "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NETO "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NETO "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NETO "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NETO "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NETO "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NETO "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Upamtite ako niste instalirali padajuće otpornike za uređivanje pinova u.ucf -u

| POVUĆI; o

| POVUCI;

Ako želite koristiti blok za bilo što, veze su sljedeće. Lijevo je broj pin bloka, a desno broj mojo pin -a koji trebate dodijeliti u svom.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Preporučuje se:

FMi_V ODBOR UNO: 6 koraka

FMi_V ODBOR UNO: HOLA AMIGOS Recite mi da li bi preguntado por que la Mayoría que realizan proyectos siempre terminan escogiendo el arduino uno? por eso decidí realizar una encuesta entre mis amigo, compañeros y profesores ¿por que escogen el arduino uno? y en

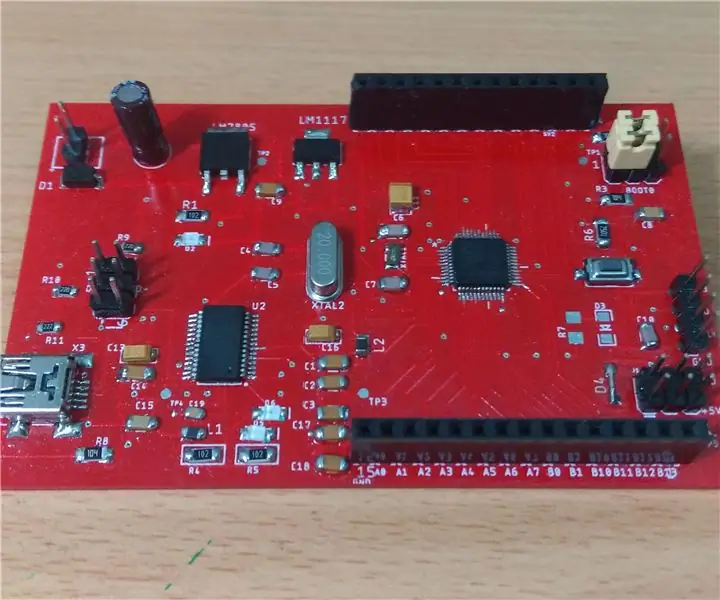

Odbor za razvoj AVR -a: 3 koraka

Odbor za razvoj AVR -a: Internet je pun projekata s Arduinom. Neko vrijeme informacije o mikrokontroleru ATMEGA328 nedostaju u svim Arduino podacima. Ovaj Inscructable želi oporaviti početak razvoja projekata pomoću AVR mikrokontrolnika

Python RF razvojni komplet: 5 koraka

Python RF Development Kit: Prije svega, želio bih dati mali uvod o tome kako sam ušao u RF stvari i zašto radim na ovom projektu. Kao student računarstva sa afinitetom prema hardveru, počeo sam pohađati neke kurseve koji bave se bežičnim signalima i

Dizajnirajte vlastiti odbor za razvoj: 5 koraka

Dizajnirajte vlastiti razvojni odbor: Napomena: Ovaj vodič uključuje besplatne informacije o dizajnu razvojne ploče, a ne besplatne sheme itd. U ovom vodiču ću vam dati informacije o tome kako možete sami dizajnirati razvojnu ploču i koji su važni savjeti i koraci. Pre zvezde

Razvojni sistem Geto programabilne logike (CPLD): 13 koraka

Razvojni sistem za geto programibilnu logiku (CPLD): Proteklih nekoliko meseci uživao sam u Razvojnom sistemu geta za AVR procesore. Zapravo, ovaj alat od gotovo nula dolara pokazao se toliko fascinantnim i korisnim da sam se zapitao je li moguće proširiti koncept na F