Sadržaj:

- Korak 1: Šta je Vivado HLS?

- Korak 2: HLS videoteka

- Korak 3: Sintetiziranje

- Korak 4: Izvođenje verzija i ostale informacije za izvoz

- Korak 5: Izvoz u Vivado IP biblioteku

- Korak 6: Sinteza i izvozna analiza

- Korak 7: Dodavanje IP biblioteke u Vivado

- Korak 8: Nadogradnja

- Korak 9: Dodatni detalji i informacije

- Korak 10: Izlaz i ulaz

- Korak 11: Povezivanje AXI registra

- Korak 12: Pragma protoka podataka

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:08.

- Zadnja izmjena 2025-01-23 14:37.

Jeste li ikada poželjeli obradu videa u stvarnom vremenu bez dodatnog kašnjenja ili u ugrađenom sistemu? Za to se ponekad koriste FPGA -i (terenski programibilni nizovi vrata); međutim, pisanje algoritama za video obradu u jezicima specifikacija hardvera poput VHDL -a ili Veriloga u najboljem je slučaju frustrirajuće. Unesite Vivado HLS, Xilinx alat koji vam omogućava programiranje u C ++ okruženju i generiranje koda jezika specifikacije hardvera iz njega.

Potreban softver:

- Vivado HLS

- Vivado

- (Ako koristite AXI registre) Vivado SDK

(Opcionalno) Primjere izrađenih u Xilinxu preuzmite ovdje:

Primjeri video zapisa Xilinx HLS

Korak 1: Šta je Vivado HLS?

Vivado HLS je alat koji se koristi za pretvaranje koda sličnog c ++ u hardverske strukture koje se mogu implementirati na FPGA. Uključuje IDE za ovaj razvoj. Nakon što završite razvoj koda za HLS, možete izvesti generirani IP u format za upotrebu sa Vivadom.

Preuzmite priložene datoteke i postavite ih blizu mjesta na kojem ćete stvarati svoj projekt. (preimenujte ih nazad u "top.cpp" i "top.h" ako imaju nasumično ime)

Korak 2: HLS videoteka

Videoteka HLS ima dokumentaciju sa referentnim dizajnom u ovom radu: XAPP1167Još jedan dobar izvor je Xilinx Wiki stranica o tome.

Pokrenite Vivado HLS.

Kreirajte novi projekat.

Uzmite datoteke koje ste preuzeli u prethodnom koraku i dodajte ih kao izvorne datoteke. (Napomena: datoteke se ne kopiraju u projekt, već ostaju gdje jesu)

Zatim pomoću gumba Pregledaj odaberite gornju funkciju.

Na sljedećoj stranici odaberite dio Xilinx koji koristite.

Korak 3: Sintetiziranje

Rješenje => Pokreni C sintezu => Aktivno rješenje

Nakon ~ 227.218 sekundi, to bi trebalo biti učinjeno. (Napomena: vaše stvarno vrijeme sinteze varirat će ovisno o mnogim faktorima)

Korak 4: Izvođenje verzija i ostale informacije za izvoz

Brojevi verzija u interakciji su s Vivadom kako biste mogli ažurirati IP u dizajnu. Ako se radi o manjoj promjeni verzije, to se može učiniti na mjestu, dok velike izmjene verzija zahtijevaju da ručno dodate novi blok i uklonite stari. Ako se vaša sučelja nisu promijenila, a ažuriranje verzije je manje, ažuriranje se može izvršiti vrši se potpuno automatski pritiskom na dugme za ažuriranje IP -a. Možete pokrenuti "report_ip_status" na Vivado tcl konzoli da vidite status vašeg IP -a.

Podesite brojeve verzija i druge informacije u Solution => Solution Settings…

Alternativno, ove postavke se mogu postaviti tokom izvoza.

Korak 5: Izvoz u Vivado IP biblioteku

Rješenje => Izvoz RTL -a

Ako u prethodnom koraku niste postavili detalje IP biblioteke, to možete učiniti sada.

Korak 6: Sinteza i izvozna analiza

Na ovom ekranu možemo vidjeti statistiku o našem izvezenom modulu, koja pokazuje da on zadovoljava naš period takta od 10ns (100MHz) i koliko svakog resursa koristi.

Kombinacijom ovoga, našeg sintetičkog izvještaja i naše analize protoka podataka, možemo vidjeti da je potrebno 317338 ciklusa takta * period od 10 ns * 14 faza cjevovoda = 0,04442732 sekunde. Što znači da je ukupna latencija dodana našom obradom slike manja od jedne dvadesete sekunde (kada radi na ciljanih 100MHz).

Korak 7: Dodavanje IP biblioteke u Vivado

Da biste koristili svoj sintetizirani IP blok, morat ćete ga dodati u Vivado.

U Vivadu dodajte IP spremište u svoj projekt tako što ćete otići u IP katalog i desnim tasterom miša odabrati "Dodaj spremište …"

Idite do direktorija projekta Vivado HLS i odaberite direktorij rješenja.

Trebao bi prijaviti IP koji je pronašao.

Korak 8: Nadogradnja

Ponekad morate unijeti promjene u svoj HLS blok nakon što ga uključite u Vivado dizajn.

Da biste to učinili, možete unijeti promjene i ponovo sintetizirati i izvesti IP s većim brojem verzije (pogledajte detalje u prethodnom koraku o promjenama velikog/manjeg broja verzije).

Nakon promjene izvoza nove verzije, osvježite svoja IP spremišta u Vivadu. To se može učiniti kada Vivado primijeti da se IP promijenio u spremištu ili se može ručno aktivirati. (Napomena, ako osvježite svoja IP spremišta nakon pokretanja, ali prije nego što se izvoz dovrši u HLS -u, IP privremeno neće biti tu, pričekajte da se završi i ponovo osvježite.)

U ovom trenutku trebao bi se pojaviti prozor s informacijom da je IP adresa promijenjena na disku i daje vam mogućnost da ga ažurirate pomoću gumba "Nadograđeno odabrano". Ako je promjena bila manja promjena verzije i nijedno sučelje nije promijenjeno, pritiskom na to dugme automatski će se stari IP zamijeniti novim, u protivnom će možda biti potrebno više posla.

Korak 9: Dodatni detalji i informacije

Sljedeći koraci pružaju više informacija o tome kako sinteza HLS -a funkcionira i što možete učiniti s njom.

Za primjer projekta koji koristi HLS sintetizirani IP blok, pogledajte ovo uputstvo.

Korak 10: Izlaz i ulaz

Izlazi i ulazi u konačni IP blok određuju se analizom koju sintetizator radi o protoku podataka unutar i van gornje funkcije.

Slično kao u VHDL -u ili verilogu, HLS vam omogućuje da navedete detalje o vezama između IP -a. Ovi redovi su primjeri ovoga:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFEJS pravcem port = video_in svežanj = INPUT_STREAM #pragma HLS SUČELJE Axis port = video_out svežanj = OUTPUT_STREAM #pragma HLS SUČELJE s_axilite port = x svežanj = CONTROL_BUS offset = 0x14 # pragma HLS SUČELJE s_axilite port = y svežanj = CONTROL_BUS offset = 0x1C

Možete vidjeti kako ove direktive utječu na portove izložene u IP bloku.

Korak 11: Povezivanje AXI registra

Da biste dobili ulaz/izlaz na/iz vašeg IP bloka na PS, dobar način za to je putem AXI sučelja.

Ovo možete navesti u svom HLS kodu, uključujući pomake koji će se kasnije koristiti za pristup vrijednosti, ovako:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS tok podataka

x = 42;

y = 0xDEADBEEF; }

Kada se pravilno povežete u Vivadu, možete pristupiti vrijednostima pomoću ovog koda u Vivado SDK -u:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Tako ćete imati 42 u x i 0xdeadbeef u y

Korak 12: Pragma protoka podataka

Unutar #pragme DATAFLOW način implementacije koda mijenja se od normalnog C ++. Kôd je usmjeren tako da se sve upute izvode u svakom trenutku u različitim dijelovima podataka (Zamislite to kao montažnu liniju u tvornici, svaka stanica radi neprekidno radeći jednu funkciju i prosljeđujući je sljedećoj stanici)

sa slike možete vidjeti da je svaka od direktiva

Unatoč tome što se čine kao normalne varijable, img objekti su zapravo implementirani kao mali međuspremnici između naredbi. Korištenje slike kao ulaza u funkciju "troši" je i čini je više neupotrebljivom. (Otuda potreba za duplikatom naredbi)

Preporučuje se:

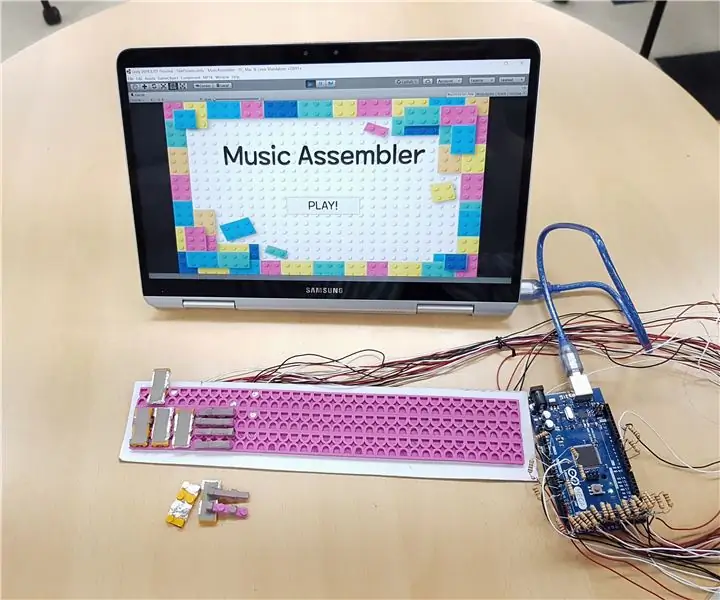

Muzički asembler: Integrisani virtuelni muzički instrument sa senzorom dodira u obliku bloka: 4 koraka

Muzički sastavljač: Integrisani virtuelni muzički instrument sa senzorom dodira u obliku bloka: Postoji mnogo ljudi koji žele da nauče svirati muzički instrument. Nažalost, neki od njih to ne započinju zbog visoke cijene instrumenata. Na osnovu toga odlučili smo napraviti integrirani sistem virtualnih muzičkih instrumenata kako bismo smanjili budžet za početak

Retro sinteza govora. Dio: 12 IoT, kućna automatizacija: 12 koraka (sa slikama)

Retro sinteza govora. Dio: 12 IoT, Kućna automatizacija: Ovaj članak je 12. u nizu o instrukcijama kućne automatizacije koji dokumentiraju kako stvoriti i integrirati IoT Retro uređaj za sintezu govora u postojeći sistem kućne automatizacije, uključujući svu potrebnu softversku funkcionalnost koja omogućuje

Mario Solarni monitor bloka pitanja: 7 koraka (sa slikama)

Mario Question Block Solar Monitor: Na krovu imamo sistem solarnih panela koji za nas proizvodi električnu energiju. Bila je to velika investicija unaprijed i polako se vraća s vremenom. Uvijek sam na to gledao kao na novčić koji pada u kantu svakih nekoliko sekundi kad izađe sunce. Da

Sinteza analognog zvuka na vašem računaru: 10 koraka (sa slikama)

Sinteza analognog zvuka na vašem računaru: Kao zvuk onih starih analognih sintetizatora? Želite li se igrati s jednim u svoje vrijeme, na svom mjestu, koliko god želite, BESPLATNO? Evo gdje se ostvaruju vaši najluđi Moogovi snovi. Možete postati elektronski umjetnik ili jus

Rastavite transformator E-bloka: 6 koraka

Rastavite transformator E-bloka: Planirao sam nabaviti gitaru, ali nedostajala mi je emajlirana žica. Pokušavajući to učiniti bez kupnje bilo čega, razmišljao sam neko vrijeme i došao na ideju da ga izvadim iz transformatora za svoj stari rotator antene. Nažalost, g