Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:07.

- Zadnja izmjena 2025-01-23 14:37.

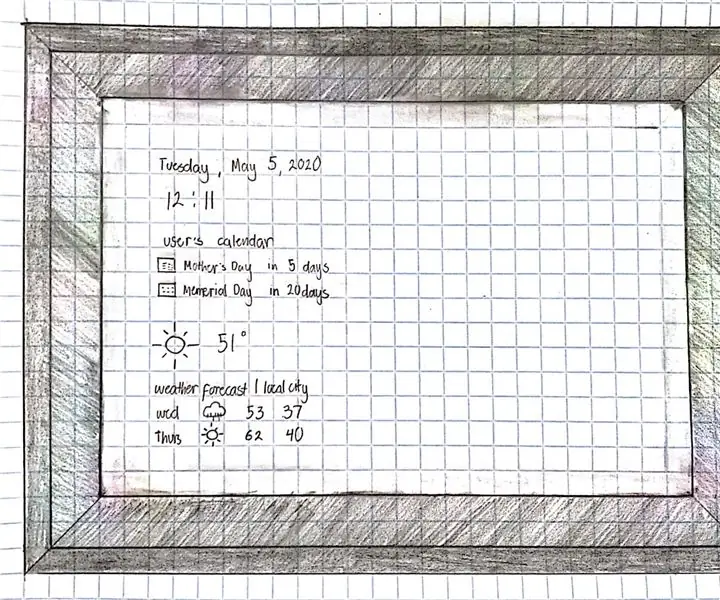

Cilj ovog projekta je stvoriti funkcionalnost prikaza slike pametnog ogledala. Ogledalo može prikazati prognoze (sunčano, djelomično sunčano, oblačno, vjetrovito, kiša, grmljavina i snijeg) i vrijednosti temperature od -9999 ° do 9999 °. Vrijednosti predviđanja i temperature su teško kodirane kao da oponašaju njihovo raščlanjivanje iz vremenskog API -ja.

Projekt koristi ploču Zynq-Zybo-7000 sa FreeRTOS-om i koristi Vivado 2018.2 za dizajniranje i programiranje hardvera.

Dijelovi:

Zynq-Zybo-7000 (sa FreeRTOS-om)

19 LCD (640x480)

VGA kabel

12 "x 18" ogledalo od akrila

Korak 1: Konfiguriranje Vivada

Preuzmite Vivado 2018.2 s Xilinxa i koristite licencu Webpack. Pokrenite Vivado i "Create New Project" i dajte mu ime. Zatim odaberite "RTL Project" i označite "Ne navodite izvore trenutno". Prilikom odabira dijela, odaberite "xc7z010clg400-1" i pritisnite "Završi" na sljedećoj stranici.

Korak 2: Pakiranje IP -a VGA upravljačkog programa

Dodajte datoteku vga_driver.sv u izvore dizajna. Zatim kliknite "Alati" i odaberite "Kreiraj i pakiraj novi IP". Odaberite "Pakirajte svoj trenutni projekt." Zatim odaberite IP lokaciju i "Uključi.xci datoteke." Kliknite na "OK" na skočnom prozoru, a zatim na "Finish".

Na stranici "Koraci pakiranja" idite na "Pregled i paket" i odaberite "Paket IP".

Sada bi vga_driver trebao biti dostupan kao IP blok.

Korak 3: Zynq IP

U odjeljku "IP integrator" odaberite "Kreiraj dizajn bloka". Dodajte "ZYNQ7 procesni sistem" i dvaput kliknite blok. Kliknite "Uvoz XPS postavki" i učitajte datoteku ZYBO_zynq_def.xml.

Zatim, pod "PS-PL Configuration" otvorite padajući izbornik za "AXI Non Secure Enablement" i označite "M AXI GP0 interface".

Zatim, pod "MIO konfiguracija" otvorite padajući izbornik "Procesorska jedinica aplikacije" i označite "Tajmer 0" i "Nadzorni pas".

Na kraju, pod "Konfiguracija sata" otvorite padajući izbornik za "PL Fabric Clocks" i označite "FCLK_CLK0" na 100 MHz.

Korak 4: GPIO IP

U dizajn bloka dodajte dva GPIO bloka. GPIO -i će se koristiti za kontrolu adrese piksela i RGB komponenti piksela. Konfigurirajte blokove kako je prikazano na gornjim slikama. Nakon što dodate i konfigurirate oba bloka, kliknite "Pokreni automatizaciju veze".

GPIO 0 - Kanal 1 kontroliše adresu piksela, a kanal 2 kontroliše crvenu boju.

GPIO 1 - Kanal 1 kontrolira zelenu boju, a kanal 2 kontrolira plavu boju.

Korak 5: Blokirajte memoriju

Dodajte Block Memory Generator IP u Block Design i konfigurirajte kao što je prikazano gore. Boje piksela se zapisuju na memorijske adrese koje zatim čita VGA upravljački program. Linija adrese mora odgovarati količini piksela koji se koriste, tako da mora biti 16 bita. Podaci su također 16 bita jer postoji 16 bitova u boji. Ne marimo za čitanje bitova za potvrdu.

Korak 6: Ostali IP

U priloženom pdf -u prikazan je dovršeni dizajn bloka. Dodajte IP koji nedostaje i dovršite povezivanje. Takođe "Make Externals" za VGA izlaze u boji i vertikalne i horizontalne izlaze za sinhronizaciju.

xlconcat_0 - Povezuje pojedinačne boje kako bi formirao jedan 16 -bitni RGB signal koji se unosi u blok RAM.

xlconcat_1 - Povezuje signale kolone i reda iz VGA upravljačkog programa i dovodi ih u port B blok RAM -a. Ovo omogućava VGA upravljačkom programu da čita vrednosti boje piksela.

VDD - konstanta HIGH povezana s omogućavanjem upisivanja blok RAM -a tako da uvijek možemo na nju.

xlslice_0, 1, 2 - Kriške se koriste za razbijanje RGB signala na pojedinačne R, G i B signale koji se mogu unositi u VGA upravljački program.

Nakon što je dizajn bloka dovršen, generirajte HDL omot i dodajte datoteku ograničenja.

*Blok dizajn zasnovan je na vodiču koji je napisao benlin1994*

Korak 7: SDK

Kod koji pokreće ovaj Block Design nalazi se ispod. Init.c sadrži funkcije koje rukuju crtežom (predviđanja, brojevi, simbol stepena itd.). Glavna petlja u main.c -u je ono što se pokreće kada se ploča programira. Ova petlja postavlja vrijednosti predviđanja i temperature, a zatim poziva funkcije crtanja u init.c. Trenutno se petlja kroz svih sedam prognoza i prikazuje jednu za drugom. Preporučuje se da dodate tačku prekida u red 239 kako biste mogli vidjeti svaku sliku. Kôd je komentiran i pružit će vam više informacija.

Korak 8: Zaključak

Kako bi se poboljšao trenutni projekt, mogle bi se učitati slike predviđanja unaprijed učitavanja u obliku COE datoteka u Block Memory Generators. Dakle, umjesto da ručno crtamo prognoze kao što smo to radili u C kodu, moglo bi se pročitati slike. Pokušali smo to učiniti, ali nismo uspjeli. Mogli smo čitati vrijednosti piksela i izlaziti ih, ali stvorili su neuredne slike koje nisu bile nimalo slične onima koje smo učitali u RAM. Tehnički list Block Memory Generator je koristan za čitanje.

Projekt je u osnovi pola pametnog ogledala jer mu nedostaje aspekt internetske povezanosti. Dodavanjem ovoga dobilo bi se potpuno pametno ogledalo.

Preporučuje se:

Jednostavno beskonačno ogledalo s Arduino Gemmom i NeoPikselima: 8 koraka (sa slikama)

Lako beskonačno ogledalo s Arduino Gemmom i NeoPikselima: Gle! Pogledajte duboko u očaravajuće i varljivo jednostavno ogledalo beskonačnosti! Jedna traka LED dioda svijetli prema unutra na sendviču s ogledalom kako bi stvorila efekt beskrajnog odraza. Ovaj projekt će primijeniti vještine i tehnike iz mog uvoda Arduin

Ogledalo za elektroničku afirmaciju: 8 koraka (sa slikama)

Elektronsko ogledalo za afirmaciju: Kada se pogledate u ogledalo, kome ne bi uspjelo nekoliko riječi ohrabrenja? Izgradite ekran unutar ogledala za pomicanje prilagođenih afirmacija koje možete čitati preko vlastitog odraza. Ovaj sjajni projekt lako se sastaje sa shadowboom kupljenim u trgovini

C.Q: DIY pametno ogledalo: 5 koraka

C.Q: DIY Smart Mirror: Mi smo Katrina Concepcion i Adil Qaiser, obje studentice druge godine na WBASD STEM akademiji. Ovo je projekt s kojim bismo sarađivali i radili ga za ovogodišnju najbolju nagradu. Kada smo odlučili raditi na ovom projektu, imali smo na umu "šta bi bilo najviše

Beskonačno ogledalo sa LCD i IC senzorom: 5 koraka

Beskonačno ogledalo sa LCD i IC senzorom: Ovaj će vam projekt pokazati kako možete napraviti beskonačno ogledalo. Osnovni koncept je da LED diode koje se nalaze na ogledalu stvaraju svjetlost koja se odbija od stražnjeg ogledala do prednjeg ogledala odakle izlazi malo svjetla pa možemo vidjeti unutra i tako

Ogledalo za prepoznavanje lica sa tajnim odjeljkom: 15 koraka (sa slikama)

Ogledalo za prepoznavanje lica s tajnim pretincem: Uvijek su me zanimali uvijek kreativni tajni odjeljci koji se koriste u pričama, filmovima i slično. Stoga sam, kad sam vidio natjecanje u tajnim odjeljcima, odlučio eksperimentirati s tom idejom i napraviti ogledalo običnog izgleda koje otvara