Sadržaj:

- Korak 1: Konfigurirajte Zynq programabilnu logiku za odašiljač

- Korak 2: Konfigurirajte Zynq programabilnu logiku za prijemnik

- Korak 3: Postavite VDMA upravljački program

- Korak 4: Postavljanje mreže nanoroutera

- Korak 5: Postavite Zynq sistem za obradu podataka za prijenos podataka putem Etherneta

- Korak 6: Postavite Zynq sistem za obradu podataka za prijem podataka putem Etherneta

- Korak 7: Povežite svoje Zybo ploče s HDMI izvorom i HDMI sudoperom

- Korak 8: Alternativne ideje za poboljšanje

- Korak 9: Pristupačnost

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:07.

- Zadnja izmjena 2025-01-23 14:37.

Jeste li ikada poželjeli da svoj televizor možete povezati s računarom ili laptopom kao vanjskim monitorom, ali niste htjeli imati sve te dosadne kablove na putu? Ako je tako, ovaj vodič je samo za vas! Iako postoje neki proizvodi koji postižu ovaj cilj, DIY projekt je mnogo zadovoljniji i potencijalno jeftiniji.

Ovaj koncept se razlikuje od proizvoda kao što je chromecast, jer je namijenjen zauzimanju mjesta HDMI kabela koji se povezuje s monitorom umjesto da bude uređaj za prijenos.

Naš projekat je nastao kao završni projekat za kurs Operativnih sistema u realnom vremenu na Kalifornijskom državnom politehničkom univerzitetu, San Luis Obispo.

Cilj projekta je korištenje dvije Digilent Zybo ploče koje će djelovati kao bežično komunikacijsko sučelje između HDMI predajnog uređaja (PC, blu-ray itd.) Do HDMI prijemnog uređaja (Desktop Monitor, Projektor, TV itd.).

Jedan Digilent Zybo bit će povezan putem HDMI -a na uređaj za odašiljanje, a drugi će biti povezan putem HDMI -a na prijemni uređaj.

Bežična komunikacija će se ostvariti korištenjem bežične lokalne mreže namijenjene predajniku i prijemniku, bez usmjeravanja putem kućnog usmjerivača ili drugog takvog uređaja. Bežični modul koji se koristi za ovaj projekt je nano skretnica tplink wr802n, od kojih jedan radi kao pristupna tačka za uspostavljanje mreže, a drugi za rad kao klijent za povezivanje na mrežu. Svaki nano usmjerivač bit će povezan putem Ethernet kabela na bilo koju Zybo ploču. Kada su spojeni na ove usmjerivače, uređaji će komunicirati putem TCP -a kao da su spojeni jednim Ethernet kablom (što znači da je jedina konfiguracija potrebna za uspostavljanje veze IP adresa klijenta).

Iako je cilj projekta bio olakšati prijenos videa od 1080x720 @ 60Hz, to nije bilo moguće postići zbog ograničenja propusnosti u bežičnoj mreži i nedostatka kompresije videa u stvarnom vremenu radi smanjenja podataka potrebnih za slanje. Umjesto toga, ovaj projekt služi kao okvir za budući razvoj za postizanje ovog cilja, budući da je ozbiljno ograničio ograničenja u brzini kadrova za pravilno strujanje HDMI podataka kako je predviđeno.

Zahtjevi projekta:

2x Digilent Zybo razvojne ploče (moraju imati najmanje jedan HDMI port)

2x HDMI kablovi

2x microusb kablovi (za povezivanje Zybo -a sa računarom radi razvoja)

2x tplink wr802n nanorouters (uključujući dodatna 2x microUSB i adapter za napajanje u zidnoj utičnici)

2x Ethernet kabel

*** Napomena: Ovaj vodič pretpostavlja poznavanje dizajnerskog paketa Vivado i iskustvo stvaranja novog projekta i dizajna blokova. ***

Korak 1: Konfigurirajte Zynq programabilnu logiku za odašiljač

Naš pristup razvoju programabilne logike predajnika bio je izvođenje hdmi-to-hdmi prenosa sa računara na monitor koristeći dva bloka za video zapis s direktnim pristupom memoriji (VDMA), jedan za pisanje i jedan za čitanje.

Oba su odabrana za slobodni rad, 3 frame-buffer (0-1-2). Budući da je video jezgro optimizirano za 60 sličica u sekundi, to znači da će VDMA upisivati ili čitati u novi okvir svakih 16,67 ms ovim redoslijedom: 0, 1, 2, 0, 1, 2, 0, 1, 2. Lokacije DDR memorije za svaki okvir su različite za dva VDMA -a jer više nisu međusobno sinkronizirane. Umjesto toga, hardverski mjerač vremena (TTC1), konfiguriran za 60 Hz, koristi se za sinhronizaciju kretanja podataka između dvije memorijske lokacije.

Gornja slika prikazuje 3 kadra, njihove dimenzije i količinu memorije koja je potrebna (desno od okvira). Ako dodijelimo VDMA za pisanje ovim memorijskim lokacijama, tada možemo dodijeliti čitane VDMA memorijske lokacije izvan ovog skupa, recimo počevši od 0x0B000000. Svaki okvir se sastoji od 1280*720 piksela, a svaki piksel sastoji se od 8 bitova crvene, zelene i plave boje za ukupno 24 bita. To znači da se okvir sastoji od 1280*720*3 bajta (2,76 MB).

Unutar tajmera IRQ, koji je opisan u postavkama VDMA upravljačkog programa, će rukovati kopiranjem podataka između dvije memorijske lokacije VMDA. VDMA pruža pokazivač na trenutni okvir na koji se piše ili čita. Okvir je predstavljen posebnim sivim kodom, koji se pretvara u softver. Definicije sivog koda za konfiguraciju međuspremnika s 3 okvira mogu se pronaći u Vodiču za proizvode AXI VDMA u dodatku C.

Ovo nam omogućava kopiranje zapisanog sadržaja u memoriju bez čitanja iz okvira koji se trenutno zapisuje.

*** Imajte na umu da se pročitani VDMA ne koristi pri slanju podataka preko bežične mreže. Njegova jedina svrha je provjeriti ispravan rad kopiranja memorije iz upisnog VMDA. VMDA za čitanje bi trebao biti onemogućen. ***

Evo koraka za stvaranje bloka dizajna odašiljača:

- Prilikom stvaranja novog projekta, dobro je dodijeliti projektu čip ili ploču. Ova veza opisuje kako dodati nove datoteke ploče u direktorij Vivado i povezati ispravnu ploču s vašim projektom. To će vam dobro doći prilikom dodavanja bloka Processing System i prelaska sa hardvera na softver (SDK strana).

-

Dodajte sljedeće blokove:

- dvi2rgb

- Video u Axi4-stream

- Regulator vremena

- axi4-stream za video izlaz

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Čarobnjak za sat

- Konstantno

- Zynq sistem za obradu

- Prilikom dodavanja sistema za obradu, kliknite "Pokreni automatizaciju bloka" na gornjoj traci zelene boje i provjerite je li odabrana opcija "Primijeni unaprijed postavljene ploče". Ostalo ostavite kao zadano.

- Slike svakog prozora za konfiguraciju bloka mogu se pronaći na gornjim slikama. Ako ne vidite sliku za određeni prozor, ostavite je kao zadanu.

-

Počnite s konfiguriranjem Zynq Processing sistema:

- U konfiguraciji PS-PL AXI Non Secure Omogući GP Master AXI, omogućite M AXI GP0 interfejs

- U PS-PL konfiguraciji HP Slave AXI sučelje omogućite i HP0 i HP1

- U MIO konfiguraciji Provjerite je li ENET0 omogućen u I/O periferijama, zatim Jedinica procesorske aplikacije, omogućite Timer0

- U konfiguraciji sata PL Fabric Clocks omogućite FCLK_CLK0 i postavite na 100 MHz.

- Pritisnite U redu

- Prije nego što kliknete "Pokreni automatizaciju veze", svakako spojite video blokove kako je prikazano na gornjoj slici dizajna TX bloka. Morat ćete preimenovati konstantu u VDD i postaviti vrijednost na 1. Povežite video blokove u skladu s tim.

- Učinite HDMI TMDS sat i pinove podataka vanjskim na blokovima rgb2dvi i dvi2rgb

- Kreirajte ulazni i izlazni port za signal detekcije vrućeg priključka (HPD) i povežite ih zajedno, oni su definirani u datoteci ograničenja

-

Sat piksela se oporavlja iz TMDS_Clk_p, koji je kreiran u datoteci ograničenja. To će biti 74,25 MHz u skladu sa 720p rezolucijom. Važno je spojiti sat piksela (iz bloka dvi2rgb) na sljedeće pinove:

- vid_io_in_clk (vid u bloku axi toka)

- vid_io_out_clk (axi tok prema video izlazu)

- clk (kontroler vremena)

- PixelClk (rgb2dvi)

- *** Napomena: Trenutno, da biste aktivirali oporavak sata piksela, HDMI rx i tx konektori moraju biti priključeni u aktivni izvor/sudoper. Jedan od načina da se to zaobiđe je odvajanje video rx i tx blokova u različite domene takta (drugim riječima, generiranje novog takta od 74,25 MHz za napajanje u tx blok). ***

- Zatim postavite čarobnjaka za sat tako da imate ulaz od 100 MHz (globalni izvor međuspremnika) i 3 izlazna takta pri 50 MHz (AXI-Lite sat), 150 MHz (sat AXI4-Stream), 200 MHz (dvi2rgb RefClk pin).

- Priključite pin sistema za obradu FCLK_CLK0 na ulaz čarobnjaka za sat

- Na ovom mjestu kliknite "Pokreni automatizaciju veze" na zelenoj traci pri vrhu prozora za dizajn. Bilo bi dobro da to radite jedan po jedan blok i slijedite gornju sliku dizajna TX bloka.

- Alat će pokušati dodati AXI Interconnect, koji djeluje kao master/slave interkonekcija za blokove koji koriste AXI-Lite sabirnicu (VDMA i GPIO).

- Također će se dodati AXI SmartConnect, koji djeluje kao glavna/podređena veza za AXI4-Stream i procesorska sučelja visokih performansi koje koristi VDMA (Stream to Memory Map i obrnuto).

- Alat će dodati i Vraćanje sistema procesora. Uvjerite se da je ovo spojeno samo na VDMA -e, GPIO -e i procesorske blokove. Nemojte ga povezivati s bilo kojim video blokovima (npr. Dvi2rgb, kontroler vremena, video za prijenos itd.)

- Nakon što je automatizacija povezivanja dovršena, provjerite da se veze podudaraju s onima na slici dizajna TX bloka. Primijetit ćete dodatni blok sistemske ILA koji nije spomenut. Ovo služi samo za otklanjanje grešaka i za sada nije potrebno. Koristi resetiranje procesora 150M, pa ni to nije potrebno. Gdje god vidite male zelene "bubice" na autobusima, to je zbog međunarodne međunarodne pomoći i može se zanemariti.

- Posljednji korak je desni klik na dizajn bloka u stablu izvora projekta i odabir "Create HDL Wrapper". Ako planirate dodati logiku u omot, ona će se prebrisati svaki put kada se ovo odabere.

- Pogledajte odjeljak Postavljanje upravljačkog programa VDMA za detalje o SDK strani.

Sat i resetiranje

Otkrio sam da su najvažniji aspekti svakog programabilnog logičkog projekta pažljivo razmatranje domena takta i signali za resetiranje. Ako su oni ispravno konfigurirani, dobro ćete uspjeti u dizajnu.

Sat i vrijeme piksela su zaključani

Da biste provjerili jesu li određeni signali aktivni, dobro je povezati ove signale sa LED diodama (satovi, resetiranja, brave itd.). Dva signala koja sam smatrao korisnim za praćenje na ploči odašiljača bili su sat piksela i signal "zaključavanja" na bloku AXI4-Stream to video out, koji vam govori da je vrijeme video zapisa sinhronizirano s kontrolerom vremena i video izvorom podataka. Dodao sam logiku omotu dizajnerskog bloka koji prati sat piksela koristeći signal PixelClkLocked na bloku dvi2rgb kao reset. Ovdje sam priložio datoteku kao hdmi_wrapper.v. Datoteka ograničenja je takođe priložena ovdje.

Korak 2: Konfigurirajte Zynq programabilnu logiku za prijemnik

Programabilni logički blok za prijemnik je jednostavniji. Ključna razlika, osim nedostajućih HDMI ulaznih blokova, je nedostatak oporavljenog sata piksela. Iz tog razloga moramo generirati vlastiti iz čarobnjaka za sat. Ovaj dizajn bi trebao biti urađen u odvojenom projektu od predajnika. Za naše potrebe, prijemnik je slijedio ploču Zybo 7Z-20, dok je odašiljač slijedio ploču Z7-10. FPGA -e na pločama su različite pa … budite oprezni.

Evo koraka za stvaranje bloka dizajna prijemnika:

-

U dizajn dodajte sljedeće ip blokove:

- Regulator vremena

- AXI4-Stream na video izlaz

- RGB na DVI

- AXI VDMA

- AXI GPIO

- Processing System

- Čarobnjak za sat

- Konstantno (VDD postavljeno na 1)

- Slijedite isti obrazac za konfiguriranje ovih blokova kao i odašiljač. Ovdje su uključene slike značajnih razlika u konfiguraciji. Ostali ostaju isti kao i odašiljač.

- Konfigurirajte VDMA za ovaj dizajn samo za čitanje kanala. Onemogućite kanal za pisanje.

-

Čarobnjak za sat treba biti konfiguriran za sljedeće izlaze:

- clk_out1: 75 MHz (sat piksela)

- clk_out2: 150 MHz (stream stream)

- clk_out3: 50 MHz (axi-lite sat)

- Povežite video blokove kako je prikazano na slici dizajna RX bloka.

- Zatim pokrenite automatizaciju veze koja će dodati blokove AXI Interconnect, AXI SmartConnect i System Reset i pokušati uspostaviti odgovarajuće veze. Idite polako ovdje kako biste bili sigurni da ne izvodi neželjene veze.

- Učinite HDMI TMDS sat i pinove podataka vanjskim na bloku rgb2dvi

- Nema potrebe za signalom vrućeg priključka na ovom dizajnu.

Korak 3: Postavite VDMA upravljački program

Postavljanje različitih blokova koji su konfigurirani putem AXI-Lite sučelja najbolje se vrši pomoću demo projekata uključenih u BSP kao referencu. Nakon izvoza dizajnerskog hardvera i pokretanja SDK -a iz Vivada, poželjet ćete dodati novi paket podrške za ploču i uključiti biblioteku lwip202 u prozor za postavke BSP -a. Otvorite datoteku datoteke system.mss sa BSP -a i vidjet ćete periferne upravljačke programe prisutne u dizajnu vašeg bloka. Opcija "Uvezi primjere" omogućuje vam uvoz demo projekata koji koriste ove periferne uređaje i na taj način vam pokazuje kako ih konfigurirati u softveru pomoću dostupnih upravljačkih programa Xilinx (pogledajte sliku u prilogu).

Ovo je metoda korištena za konfiguriranje VDMA -e, mjerača vremena i prekida i GPIO -a. Ovdje je uključen izvorni kod i za prijenos i za prijem. Razlike su gotovo isključivo u main.c.

*** NAPOMENA: Budući da sistem nije bio potpuno funkcionalan u vrijeme pisanja ovog vodiča, izvorni kod u ovom odjeljku ne uključuje kôd bežične mreže. Nekoliko grešaka treba riješiti kao rezultat kombiniranja projekata prijenosa/primanja video jezgre s projektima prijenosa/primanja na mreži. Stoga ih ovaj vodič za sada tretira zasebno. ***

Funkcija rukovatelja TX prekidima (IRQHandler)

Ova funkcija čita sive kodove koje pružaju VDMA za čitanje i pisanje putem GPIO blokova. Sivi kodovi se pretvaraju u decimalne i koriste se za odabir osnovne memorije okvira trenutnog okvira. Kopirani okvir je prethodni okvir u odnosu na onaj na koji VDMA zapisuje (npr. Ako VDMA piše u okvir 2, kopiramo okvir 1; ako zapisuje u okvir 0, premotavamo i čitamo iz okvira 2).

Ova funkcija snima samo svaki 6. okvir kako bi smanjila broj sličica na 10 Hz, a ne na 60 Hz. Gornja granica mreže je 300 Mbps. Pri 10 sličica u sekundi potrebna je propusnost od 221,2 Mbps.

Komentiranje/uklanjanje komentara iz dva retka u ovoj funkciji omogućit će korisniku da pređe u HDMI passthru način radi otklanjanja grešaka/testiranja (kôd se komentira kako bi označio odgovarajuće retke). Trenutno kopira okvir na memorijsku lokaciju koju koristi ethernet kôd.

Funkcija rukovatelja prekidima RX (IRQHandler)

Ova funkcija je vrlo slična TX funkciji, ali kopira iz 2 međuspremnika FIFO koji koristi ethernet za upisivanje dolaznih podataka. Ethernet kôd označava u koji okvir se upisuje FIFO, podaci se kopiraju iz suprotnog okvira. Podaci se kopiraju u okvir neposredno iza onog koji čita VDMA kako bi se izbjeglo kidanje.

Korak 4: Postavljanje mreže nanoroutera

Da biste stvorili mrežu pomoću TPlink nano skretanja, uključite ih pojedinačno i povežite se sa zadanim Wi -Fi SSID -om za uređaje. Više informacija o postavkama konfiguracije za ovaj uređaj možete pronaći u korisničkom priručniku za uređaj.

Postavite jedan od uređaja kao pristupnu točku, to će djelovati kao primarna veza za mrežu. Provjerite dajte ime mreži i zabilježite ime te onemogućite DHCP (ne želimo da usmjerivač dinamički konfigurira IP adrese, želimo da Zybo ploče tansmittera i prijemnika same postave svoje IP adrese kako bi bile dosljedne). Nakon konfiguriranja provjerite da li se uređaj ponovno pokreće i uspostavlja ovu mrežu.

Postavite drugi uređaj kao klijent i provjerite je li povezan s mrežnim SSID -om koji ste postavili s prvim nano usmjerivačem. Još jednom provjerite je li DHCP onemogućen za klijenta.

Nakon što klijent završi i ponovno pokrene sistem, trebao bi se povezati s nano skretačem pristupne točke (ako se to ne dogodi, vjerovatno postoji problem u vašoj konfiguraciji jednog od uređaja). Primijetit ćete da će LED svjetlo na klijentu biti čvrsto nakon što se spoji na pristupnu točku.

LED pristupna točka nanoroutera će vjerojatno nastaviti treperiti u ovom trenutku, to je u redu! Trepćuće svjetlo znači da nije povezano s drugim uređajem sa njegovog Ethernet porta, a nakon što se spoji na konfigurirani Zybo LED dioda će ostati svijetla što ukazuje na uspješnu mrežnu vezu.

Sada kada smo postavili naše nano skretnice, imamo bežičnu mrežu koja će nam omogućiti komunikaciju. Važna napomena je da nam naš način konfiguracije za nano usmjerivače (kao pristupnu točku i klijenta) omogućuje komunikaciju s odašiljačke Zybo ploče na prijemnu Zybo ploču kao da su dvije povezane jednom Ethernet žicom. To čini naše postavljanje mreže manje teškim, jer bi alternativa vjerojatno uključivala konfiguriranje Zybo ploča za eksplicitno povezivanje s poslužiteljem zajedno s predviđenom vezom.

Nakon što su oba uređaja postavljena, nano skretnice su konfigurirane i spremne za implementaciju u vašu WIDI mrežu. Ne postoji posebno uparivanje između nano usmjerivača i Zybo ploča, jer će pristupna točka ili klijent raditi za prijenosni ili prijemni uređaj.

Korak 5: Postavite Zynq sistem za obradu podataka za prijenos podataka putem Etherneta

Za prijenos HDMI podataka s jedne Zybo ploče na drugu, moramo uključiti Ethernet protokol u naš VDMA upravljački program. Naš cilj ovdje je strujanje pojedinačnih video okvira kroz Ethernet periferiju u sistemu za obradu, po zadanoj brzini koja je u skladu s propusnošću naše mreže. Za naš projekt koristili smo TCP koji obezbjeđuje LwIP API od golih metala. Budući da su oboje članova projekta relativno neiskusni u vezi s uslužnim programima za umrežavanje, ovaj izbor je napravljen bez potpunog prepoznavanja implikacija i ograničenja vezanih za TCP. Glavni problem s ovom implementacijom bila je ograničena propusnost i činjenica da zaista nije dizajnirana za potrebe prenošenja velike količine podataka. Alternativna rješenja za zamjenu TCP -a i poboljšanje u ovom projektu bit će razmotrena kasnije.

Kratak opis TCP -a s LwIP -om: Podaci se šalju preko mreže u paketima veličine tcp_mss (TCP maksimalna veličina segmenta), koja je općenito 1460 bajtova. Pozivanje tcp_write će uzeti neke podatke na koje upućuje pokazivač i konfigurirati pbufs (međuspremnike paketa) za držanje podataka i pružanje strukture za TCP operacije. Maksimalna količina podataka koja se može staviti u red odjednom postavljena je kao tcp_snd_buf (TCP pošiljateljski međuspremnik). Budući da je ovaj parametar 16 -bitni broj, ograničeni smo na veličinu međuspremnika za slanje od 59695 bajta (u međuspremniku za slanje potrebno je neko popunjavanje). Nakon što se podaci stave u red, tcp_output se poziva da započne prijenos podataka. Prije slanja sljedećeg segmenta podataka, imperativ je da su svi prethodni paketi uspješno preneseni. Ovaj proces se vrši pomoću funkcije recv_callback, jer je to funkcija koja se poziva kada se potvrda vidi sa prijemnika.

Korištenje primjera projekata u Vivado SDK -u vrlo je korisno za učenje o načinu rada LwIP TCP -a i dobra je polazna osnova za početak novog projekta.

Postupak za WiDi prijenosni uređaj je sljedeći:

- Inicijalizirajte TCP mrežu koristeći gole metalne pozive funkcije upravljačkog programa LWIP.

- Navedite sve funkcije povratnog poziva potrebne za mrežne operacije.

- Povežite se sa WiDi prijemnikom povezivanjem na njegovu IP adresu i port (naša konfiguracija: IP adresa prijemnika je 192.168.0.9, povežite se na port 7).

- Kad tajmer upravljačkog programa VDMA istekne, unesite TX ISR.

- Odredite trenutni međuspremnik okvira za pristup na osnovu VDMA sivog koda

- Postavite prvi segment podataka u red čekanja u TCP međuspremniku za slanje

- Iznesite podatke i ažurirajte lokalne varijable kako biste pratili koliko je podataka poslano u trenutnom okviru.

- Nakon dostizanja primljenog povratnog poziva (poziv funkcije nakon što odašiljač primi potvrdu o preuzimanju podataka), postavite u red sljedeći segment podataka.

- Ponavljajte korake 7 i 8 dok se ne pošalje cijeli okvir.

- Vratite se u stanje mirovanja kako biste sačekali sljedeći prekid brojača kako bi naznačili da je novi okvir spreman (Natrag na korak 4).

Postavite postavke LwIP paketa za podršku ploče kao što je prikazano na gornjoj slici. Sve su vrijednosti zadane, osim za tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Takođe imajte na umu da se detaljno otklanjanje grešaka može postići promjenom BSP parametara za grupu debug_options.

Korak 6: Postavite Zynq sistem za obradu podataka za prijem podataka putem Etherneta

Zybo razvojna ploča koja će djelovati kao bežični prijemnik funkcionirat će slično uređaju za odašiljanje. Postavke paketa podrške za ploču za LwIP bit će identične onima u prethodnom koraku.

Uređaj će primati pakete koji sadrže segmente video okvira iz nano skretanja i kopiraće podatke video okvira u međuspremnik s tri okvira za prijemni VDMA. Kako bi se izbjeglo prepisivanje bilo kakvih podataka, dvostruki međuspremnik podataka (mi ćemo ga nazivati mrežni bafer) koristi se pri prikupljanju podataka iz nano skretanja, tako da se mrežni promet može nastaviti prenositi dok se prethodni cijeli video okvir kopira u VDMA međuspremnik.

Postupak za WiDi prijemni uređaj zahtijeva dva zadatka, od kojih jedan prima ethernet podatke, a drugi je kopiranje video okvira iz mrežnog međuspremnika u međuspremnik VDMA s tri okvira.

Zadatak Ethernet prijema:

- Inicirajte TCP mrežu koristeći gole metalne pozive funkcije upravljačkog programa LWIP (postavljanje s IP adresom na koju će se odašiljač povezati, 192.168.0.9 u našoj)

- Navedite sve funkcije povratnog poziva potrebne za mrežne operacije.

- Nakon primljenog ethernet paketa, kopirajte paketne podatke u trenutni mrežni međuspremnik, povećajte trenutne akumulirane podatke.

- Ako paket ispunjava međuspremnik mrežnog okvira, nastavite na korake 5 i 6. U suprotnom, vratite se na korak 3 za ovaj zadatak.

- signal da bi zadatak VDMA trostrukog međuspremnika trebao kopirati iz novozavršenog mrežnog međuspremnika.

- Prebacite se na drugi mrežni međuspremnik i nastavite prikupljati podatke putem etherneta.

- Neaktivan dok se ne primi novi ethernet paket (korak 3).

Kopirajte mrežni međuspremnik u VDMA međuspremnik s tri okvira:

- Kad tajmer upravljačkog programa VDMA istekne, unesite RX ISR.

- Odredite trenutni međuspremnik okvira za pristup na osnovu VDMA sivog koda.

- Odredite koji će se mrežni međuspremnik kopirati u VDMA međuspremnik i kopirajte te podatke

Korak 7: Povežite svoje Zybo ploče s HDMI izvorom i HDMI sudoperom

Sada spojite hdmi kablove i za prijemnik i za predajnik, programirajte FPGA -e i pokrenite sistem za obradu. Brzina kadrova bit će vjerojatno vrlo spora, zbog ogromnih troškova u operaciji LwIP i ograničene propusnosti. Ako postoje problemi, povežite se putem UART -a i pokušajte identificirati upozorenja ili greške.

Korak 8: Alternativne ideje za poboljšanje

Veliki problem za ovaj projekt bila je količina podataka potrebna za slanje putem WiFi -ja. To je bilo očekivano, međutim potcijenili smo utjecaj koji bi to moglo imati i rezultiralo je većim brojem slika na ekranu, a ne video sažetkom. Postoji nekoliko načina za poboljšanje ovog projekta:

- Kompresija videa u stvarnom vremenu. Komprimiranje dolaznog video feeda po kadar značajno bi smanjilo količinu podataka potrebnih za slanje preko mreže. Idealno bi bilo da se to uradi hardverski (što nije lak zadatak), ili bi se moglo uraditi softverski upotrebom drugog jezgra ARM -a za pokretanje algoritama kompresije (ovo bi zahtijevalo dodatnu analizu kako bi se osiguralo da vrijeme funkcionira). Na webu smo pronašli neke komponente kompresije videa u stvarnom vremenu otvorenog koda, ali većinu čine IP.

- Implementacija Ethernet toka u hardveru, a ne u softveru. Bilo je puno režijskih troškova zbog nedostatka prostora na raspolaganju za slanje odlaznih podataka u redu odašiljača, zbog ograničenja veličine segmenta. Mnogo učinkovitiji proces je korištenje AXI Ethernet IP -a s FIFO baferom ili DMA -om za unos podataka u njega. To bi smanjilo dodatni prtljag iz LwIP TCP -a i omogućilo veći protok podataka.

Korak 9: Pristupačnost

Rezultirajući proizvod ovog WiDi projekta trebao bi biti potpuno integriran, kompaktan par uređaja koje bi korisnik mogao spojiti na bilo koji HDMI izvor, a zatim bežično prenijeti video prijenos na zaslon s HDMI sposobnošću. Uređaji bi imali Zynq-7000 SoC koji se nalazi na Zybo referentnoj ploči i uključivali bi mrežni hardver koji se nalazi u nano-usmjerivačima TP-Link. U idealnom slučaju, korisnik bi mogao kontrolirati modul za prijenos s diskretne lokacije unutar ciljnog operativnog sistema, uz malu potrebu za značajnim tehničkim sposobnostima.

Sigurnost i povezivanje

Uređaji bi također trebali uključivati sigurnost transportnog sloja (TLS) i imati ograničenu mogućnost automatskog povezivanja, kako zbog privatnosti. Namjera dizajnera je da povezivanje s ekranom putem bežičnog sučelja namjernom akcijom u ime korisnika izbjegne pogrešno emitiranje osjetljivog materijala.

Sadašnji status

Do ovog trenutka stanje projekta je još uvijek u tijeku. Da bi trenutni krajnji korisnik imao koristi od ovog vodiča, on ili ona mora imati dobro tehničko razumijevanje dizajna ugrađenog sistema i mora biti upoznat sa programiranim hardverom i ugrađenim softverom koji rade zajedno.

Podaci koji se šalju preko mreže u ovom trenutku nisu šifrirani i pretpostavlja se da su sirovi prijenos TCP/IP paketa.

Video jezgreni projekt uspješno je testiran i za prijenos i za prijem. S druge strane, uspostavljena je bežična veza između dvije zybo ploče i uspješno su poslani podaci testnog okvira. Ipak je potrebno kombinirati mrežni kôd sa svakim jezgrom video projekta i testirati prijenos stvarnih video okvira.

Preporučuje se:

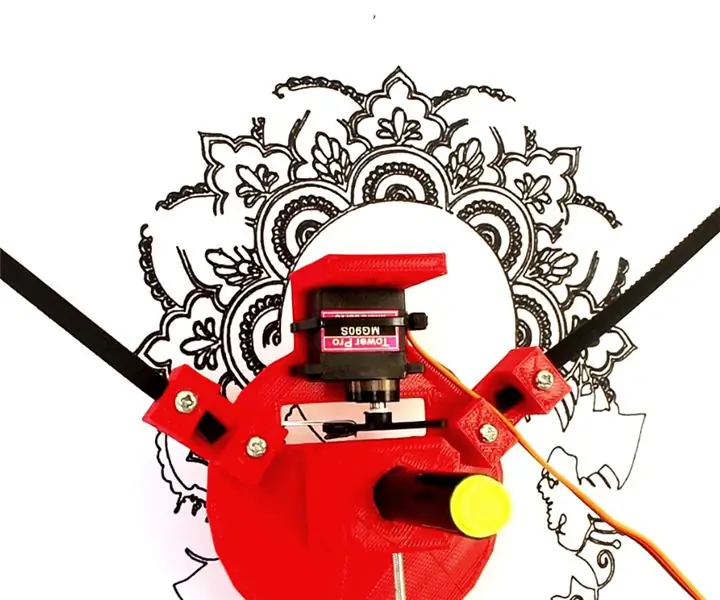

MXY ploča - niskobudžetna robotska ploča za crtanje XY plotera: 8 koraka (sa slikama)

MXY ploča - Robotska ploča za crtanje niskobudžetnih XY plotera: Moj cilj je bio dizajnirati mXY ploču tako da bude niskobudžetna mašina za crtanje XY plotera. Zato sam dizajnirao ploču koja olakšava onima koji žele napraviti ovaj projekt. U prethodnom projektu, koristeći 2 komada Nema17 koračnih motora, ova ploča koristi

Quadcopter pomoću Zybo Zynq-7000 ploče: 5 koraka

Kvadrokopter koristeći Zybo Zynq-7000 ploču: Prije nego počnemo, evo nekoliko stvari koje želite za projekt: Popis dijelova1x Digilent Zybo Zynq-7000 ploča 1x okvir za četverokopter koji može montirati Zybo (priložena datoteka Adobe Illustrator za lasersko rezanje) 4x Turnigy D3530/ 14 1100KV motori bez četkica 4x

UDuino: Vrlo niska cijena Arduino kompatibilna razvojna ploča: 7 koraka (sa slikama)

UDuino: Vrlo niska cijena Arduino kompatibilna razvojna ploča: Arduino ploče odlične su za izradu prototipova. Međutim, oni postaju prilično skupi ako imate više istovremenih projekata ili vam je potrebno mnogo kontrolnih ploča za veći projekt. Postoje neke odlične, jeftinije alternative (Boarduino, Freeduino), ali

Razvojna ploča Atmega16/32 sa LCD -om: 8 koraka

Razvojna ploča Atmega16/32 s LCD -om: Ova instrukcija prikazuje kako napraviti vlastitu razvojnu ploču za procesore Atmega16 ili Atmega32. Internet je pun domaćih razvojnih ploča, ali mislim da je ostalo prostora za još jednu. Ova ploča je bila jako korisna u mom projektu

18 Pin PIC razvojna ploča: 3 koraka

18 Pin PIC Development Board: Dugo sam se igrao sa Microchip PIC -ovima, ali uvijek sam se snalazio bez nekog oblika razvojne ploče. U tu svrhu dizajnirao sam osnovnu ploču za koju sam se nadao da ću dobiti neke podatke. Još nisam napravio ovu ploču jer čekam ki