Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:04.

- Zadnja izmjena 2025-01-23 14:37.

U prošlosti sam napisao vodič o tome kako izgraditi računalo zasnovano na Z80 i dizajnirao sam krug što je moguće pojednostavljenije kako bi se mogao izgraditi što je moguće lakše. Napisao sam i mali program koristeći istu ideju jednostavnosti. Ovaj dizajn je prilično dobro funkcionirao, ali nisam bio potpuno zadovoljan s njim. Počeo sam s prepisivanjem programa koji mu je omogućio programiranje za vrijeme izvođenja. Ovo mi je omogućilo da testiram komade koda, a da ga ne moram posvetiti EEPROM -u, što bi zauzvrat zahtijevalo od mene da reprogramiram EEPROM. Ovo mi nije zvučalo kao zabavna ideja. Tada sam počeo razmišljati o memorijskim prostorima. Ako želim spojiti dio hardvera (uglavnom IO), komad koda bi potencijalno mogao premašiti količinu memorijskog prostora dostupnog sistemu. Upamtite, dizajn je koristio samo donji bajt sabirnice adresa, a zatim je donji bit visokog bajta korišten za odabir između prostora ROM -a i RAM -a. To je značilo da imam samo 253 bajta prostora za korištenje. Možda se pitate zašto 253 umjesto 256. To je zato što moj novi kod ubacuje tri bajta podataka na kraju pisanog programa (to će biti obrađeno kasnije, jer sam ga izmijenio da bih radio na novom dizajnu).

n

Vratio sam se na stare sheme da vidim šta se još dešava. Otkrio sam mali nedostatak u krugu za odabir memorije, koji ću pokriti kad tamo stignem. Pojednostavljena verzija: svi zahtjevi za pisanje bi zapravo prošli, iako se uvijek stavljaju u RAM. Ovo vjerovatno nije bilo razlog za brigu, ali ovaj put sam htio to učiniti kako treba. I s tim sam počeo crtati novu shemu. Dvije slike priložene ovoj stranici su prije i poslije stvarnog kola. Očistio sam toliko ožičenja od špageta, to nije smiješno.

n

Ako ste slijedili moj izvorni podnesak i planirate slijediti ovaj, mrzit ćete me. Ako tek počinjete, imate sreće. Samo uzmite dijelove s popisa (ili njihov ekvivalent) i slijedite ih.

Potrošni materijal:

LM7805 - 5 -voltni regulatorZ80 - CPU; mozak sistemaAT28C64B - EEPROM. "Trajno" skladište podataka koje se koristi za firmver računaraIDT6116SA - SRAM; koristi se za pohranu korisničkog koda i /ili opće pohrane podatakaNE555 - Sistemski sat74HC374 - Oktalna D -zasuna sa /OE; koristi se kao ulazni čip74LS273 - Oktalna D -zasuna sa /MR; izlazni čipTLC59211 - LED upravljački čip (koristi se tako da 74LS273 može pokretati LED diode, jer sam po sebi nije sposoban za trenutni izlaz) MC14572 - Ovo je čip "Line Driver", ali smatrao sam da je savršen za logiku upravljanja memorijom. Ima 4 pretvarača i NAND i NOR kapiju ugrađenu u 74LS32 - četvero ILI kapijuCD4001 - četverostruku NOR kapiju CD4040 - brojač od 12 stepeni talasa; Ucrtani, ali nije implementiran razdjelnik sata (za rad sistema na sporijim brzinama takta) 2 10K ohmskih otpornika - jedan se koristi u krugu mjerača vremena 555, pa za njega upotrijebite koju god vrijednost želite 4 1 ohmski otpornik - jedan se koristi za 555 timer, pa upotrijebite što god želite. Druga se koristi za pogon LED dioda, pa je i vi promijenite ako želite sabirnicu otpornika 8x330 Ohma 8x10K ohma sabirnicu otpornika11 LED - tri se koriste za status sistema, a ostalih osam su izlazi. Za 8 sam koristio prikaz stupčastog grafikona (HDSP -4836) 4 kondenzatora - dva se koriste LM7805; 0.22uF i 0.1uF. Jedan je za tajmer 555, pa koristite ono što smatrate da je ispravno. Posljednji je za resetiranje pri uključivanju; 100uF2 N. O. Tasteri - Jedan se koristi za unos, drugi za resetovanje8 SPST DIP prekidači - Unos podataka; Koristio sam Piano Key styleWire. Puno žice

n

NAPOMENA: MC14572 verzija sa rupom je zastarjela, ali verzija SMD je i dalje aktivna (čak ni status "nije za novi dizajn"), pa ćete možda morati kupiti ploču kako biste je mogli koristiti. Drugi 74LS32 može se koristiti umjesto MC14572 (pogledajte shemu "krug odabira memorije" iz prethodne tabele)

Korak 1: Brzi pregled promjena + sheme

Kako čitati sheme: Strelica usmjerena u čip je ulaz: Ulaz>-Strelica usmjerena dalje od čipa je izlaz: Izlaz <-Autobusi koriste liniju umjesto strelice: Sabirnica |-

n

Većina čipova je izvučena sa tačnim pinout -ovima. Mali pad je izvučen na ovim čipovima. Većina čipova također ima pin brojeve i oznake. Možda ih je malo teško čitati. Olovka mi je postajala tupa.

n

Što se tiče spojeva na strujna kola, izgled novog dizajna uglavnom se ne mijenja u odnosu na original. Donji dio gornjeg bajta adrese povezao sam s memorijama, a zatim sam upotrijebio niži bit gornjeg gita (A12) za odabir RAM -a/ROM -a. To je značilo da je ROM prostor prešao sa 0000-00FF na 0000-0FFF. Ram prostor je prešao sa 0100-01FF na 1000-1FFF. Također sam zamijenio logiku kontrole memorije za bolji dizajn i dodao dvije nove LED diode statusa (i nešto logike ljepila). Također sam nacrtao (ali nisam spojio) krug razdjelnika sata. Trebalo je obavljati dvije funkcije. Očigledna funkcija je dijeljenje frekvencije takta prema dolje. Druga funkcija je za PWM (Pulse Width Modulation) funkciju, jer 555 ne generira valove s 50% radnim ciklusima. To u ovom krugu zapravo nije važno, ali ako želite koristiti sat za pokretanje nekih LED dioda, definitivno ćete primijetiti efekte (jedna (set) LED dioda će biti slabija od druge). Cijeli ostatak kola je u osnovi nepromijenjen.

Korak 2: CPU, memorija i kontrola memorije

Ovo je dio u kojem me čitatelji moje prethodne verzije mrze. U originalnoj verziji, jednostavno sam bacio dijelove na ploču na mjesto na kojem su izgledali kao da bi im nametnuli mali problem s povezivanjem. Rezultat je izgledao kao da je neko na njega izbacio tanjir špageta i bio je poput "žica!" Htio sam to malo očistiti pa sam počeo tako što sam iscrpio sve osim CPU -a, RAM -a i ROM -a. Povukao sam gotovo cijeli ulazni krug, izlazni krug i logiku ljepila. Skoro da me povrijedilo, ali bilo je potrebno. Ostavio sam sve podatkovne veze netaknutima i donji bajt sabirnice adresa. Zatim sam spojio sljedeća četiri bita sabirnice adresa (A8-A11) na ROM čip. Ovaj put sam se pobrinuo da obiđem čip kako bih ga lakše povukao za reprogramiranje. Također sam preskočio adresne veze do RAM čipa.

n

S tim u vezi, morao sam sada povezati logiku kontrole memorije. U originalnoj shemi, spojio sam liniju procesora /MREQ direktno na /CE na oba memorijska čipa, zatim sam spojio /WR na RAM -ove /WE. Zatim sam logički imao CPU -ove /RD i /MREQ ILI zajedno, kao i A9. U osnovi, postavljeno je tako da svi memorijski zahtjevi aktiviraju i RAM i ROM, ali A9 je korišten za odabir koji od čipova /OE je izabran. To je bilo u redu, a sve zato što su čipovi ostali neaktivni sve dok se ne uputi zahtjev za memorijom, a zatim bi samo jedan /OE bio aktivan za vrijeme čitanja. Ovo je spriječilo preslušavanje, ali je unijelo neugodnu nijansu. Budući da se A9 koristio samo za određivanje čipa koji ispisuje podatke i zato što je CPU imao direktan pristup RAM -u /WE pin -u, svi i svi zahtjevi za upis bi se prošli. To je bilo u redu za ROM jer je njegov način pisanja onemogućen vezanjem /WE direktno na 5V napajanje. Na RAM bi se, međutim, pisalo bez obzira na A9. To je značilo da bi pokušaj pisanja na lokaciju ROM prostora pisao na istu lokaciju u RAM prostoru.

n

Jedno rješenje za ovo bilo bi ponovno povezivanje upravljačke logike tako da CPU ima izravan pristup pinovima čipova /OE i /WE, a zatim pomoću MREQ i A12 za odabir čipova /CE -a koji će se pokretati. Išao sam na ovu ideju, ali umjesto da koristim četiri NOR kapije i pretvarač poput originalnog dizajna, pronašao sam nezgodan mali čip koji je bio savršen za taj zadatak. Morao sam stvoriti krug koji je koristio samo logička vrata dostupna u čipu, ali to je bilo dovoljno jednostavno. A12 se napaja direktno u NAND vrata i NOR vrata. /MREQ se dovodi na NOR kapiju, a njen kompliment se prenosi na NAND kapiju. NAND kapija se koristi za pogon /CE za RAM, a NOR izlaz se pretvara i koristi za pogon ROM /CE. Zbog toga /MREQ mora biti nizak prije nego što se odabere bilo koji čip, a zatim A12 bira koji će biti odabran. Sa ovim podešavanjem, sada svi zahtjevi za upisivanje na ROM neće ništa učiniti. Također štedi energiju jer je samo jedan čip aktivan umjesto oba. Što se tiče samog logičkog čipa, unutra imamo još dva neiskorištena pretvarača. Jedan će se kasnije naviknuti, ali stići ćemo tamo kad stignemo.

Korak 3: LED diode statusa sistema

Prije nego što sam započeo ovaj projekt, pokušavao sam se povezati s određenim IC -om, ali sam imao problema s tim. Nisam siguran šta se događa, upotrijebio sam LED za montiranje ploče za ispitivanje (jedan od onih sklopova koji ima ugrađen otpornik). Ovo mi je dalo nostalgičnu ideju koja se i danas koristi: LED diode statusa su označavale čita li se memorija ili se u nju piše. Trebalo je da se koristi zajedno sa ulaznom LED diodom koju sam već imao. Ulazna LED dioda je spojena na /WAIT generator signala kako bi nam ukazao da sistem čeka ulaz (stići ću, ne brinite). Razmišljao sam o dodavanju LED -a za označavanje IO zapisa, ali sam zaključio da bi promjena izlaznih LED -ova već bila odličan pokazatelj toga. Razmišljajući o tome, možda ću ga još dodati. Ipak, smatram da je korisno znati čita li se ili piše memorija. Pa, ionako je korisno za otklanjanje grešaka u programu. Zapravo sam ga jako koristio kao takav pokušavajući da pokrenem svoj program: „zašto piše u memoriju? To još ne bi trebalo da radi!”

n

Za kontrolu ovih LED dioda koristio sam quad NOR gate. Koristio sam sve kapije. Za generiranje statusnih signala korištena su samo dva, ali čip nema mogućnosti napajanja za pokretanje LED dioda. Sposobni su potopiti toliko energije, pa sam koristio druga dva NOR ulaza kao pretvarače i kao takve spojio LED diode. Budući da se jedna LED koristi za označavanje čitanja, a druga za pisanje, a zahtjev za čitanjem i pisanjem neće se pojaviti u isto vrijeme, uspio sam pobjeći koristeći samo jedan otpornik za obje LED diode. Što se tiče signala koje sam trebao dekodirati, to je također bilo dovoljno jednostavno. Htio sam da svi zahtjevi za čitanje memorije budu označeni, tako da je prvi NOR gate imao /MREQ i /RD na svojim ulazima. Status pisanja bio je malo teži, ali jednako lak. I dalje sam koristio /MREQ kao jedan ulaz, ali korištenje /WR kao drugog uzrokovalo bi manju nijansu koju sam htio izbjeći. To bi označilo SVE zahtjeve za pisanje. Želeo sam samo one koje su zaista prošle. Pa kako bih to učinio? Pa, sjetite se kako sam postavio sistem tako da se samo RAM može pisati? Koristio sam RAM -ove /CE kao drugi ulaz za NOR kapiju. To znači da će LED lampica svijetliti samo kada se odabere RAM i podnese zahtjev za upis. Što se tiče LED boje, izabrao sam narandžastu kao indikator čitanja (ali pronašao sam samo žute) i crvenu kao indikator pisanja.

Korak 4: Ulaz i izlaz

U prethodnom koraku ste možda primijetili da sam neke od ostalih komponenti već dodao na ploču. Rezervirao sam prostor kako ne bih slučajno postavio žice tamo gdje želim komponentu (stoga bih morao pronaći novu lokaciju za spomenutu komponentu). Možda ste također primijetili da sam ostavio ulazne prekidače na mjestu i ožičen do razvodnika. Odlučio sam da je originalna lokacija savršeno mjesto i odlučio sam postaviti izlazne LED diode u blizini (gore). Desno od prikaza trake nalazi se reza za unos. Iznad toga je izlazna reza, a lijevo od nje je LED upravljački program. Počeo sam povezivanjem ekrana s upravljačkim programom jer je to bilo najlakše učiniti. Zatim sam spojio prekidače na ulaznu stranu ulaznog zasuna. Zatim sam spojio izlaznu stranu izlaznog zasuna na LED upravljački program. Ovo može izgledati kao neugodna naredba za povezivanje ovih uređaja, ali to je bilo s razlogom. Ulaz izlaznog zasuna trebao je biti spojen na sabirnicu podataka, kao i izlaz ulaznog zasuna. Ideja je bila spojiti izlaze ulaznog zasuna sa ulazima izlaznog zasuna, što sam i učinio. Tada je sve što sam trebao učiniti bilo povezati taj nered sa sabirnicom podataka. Nije bilo važno kamo su te veze fizički otišle jer će sve biti električno povezane. Računar je skoro gotov.

Korak 5: Poništite i dovršite unos i izlaz

Nažalost, nema slika za ovaj korak. Slike potražite u prethodnom koraku.

n

Možda ste primijetili na posljednjoj slici prethodnog koraka da sam imao zeleno dugme i instaliran drugi logički čip. Čip je kapija ILI. Dva gejta se koriste za generisanje /WAIT signala. Pa, signal se generira pomoću OR-ing /IORQ i /RD iz procesora. Izlaz se dovodi u drugu kapiju, gdje ponovo dolazi ILI na dugme. Dugme dovodi ulaz kapije visoko, čime se izlaz dovodi visoko. Ovaj izlaz se dovodi na procesore /WAIT pin. Dok nije pritisnut, otpornik drži ulaz niskim. U početku sam koristio 10K otpornik, ali LS32 je zapravo gasio napon na ulazu. Otpornik nije pao dovoljno nisko i morao sam ga zamijeniti sa 1K. U svakom slučaju, ideja je da kada se napravi zahtjev za čitanje IO -a, prva i druga kapija ILI govore procesoru da čeka. Kada postavite ulazne prekidače na sve što želite, pritisnite dugme i to dovodi CPU iz stanja čekanja. Zelena "ulazna" LED dioda, kako sam je nazvao u jednom ranijem koraku, ožičena je tako da kad se pin /WAIT spusti, svijetli.

n

Ali još nismo završili. Ulazni japanka treba signal koji mu daje do znanja kada je unos podataka ispravan i treba ga staviti na CPU. Ovaj pin sata je aktivan visoko. Prije smo ga samo povezali s gumbom. Ovo je još uvijek valjana opcija, ali ovaj put sam odabrao da je postavim na isti izlaz kao i druga vrata ILI. Ovaj IC također ima /OE pin koji treba pokretati. Da se drži visoko, nikada ne bi umetnuo podatke u sabirnicu. Da se drži nisko, uvijek bi vozio autobus. Da bih to ispravio, jednostavno sam upotrijebio treći ulaz ILI. Ulazi su /IORQ i /RD, a izlaz ide direktno u zasun /OE.

n

Izlazna zasun također treba pokrenuti pin sata. Opet, visoko je aktivan. U mojoj shemi, nacrtao sam četvrtu ILI kapiju direktno upravljajući iglom koristeći /IORQ i /WR. To je značilo da će se igla sata držati visoko sve dok se ne upiše zahtjev za upis, a zatim će pasti nisko pa opet visoko. Ovo bi vjerovatno bilo u redu jer bi sabirnica podataka i dalje imala važeće podatke o sebi odmah nakon pokušaja upisivanja, ali s inženjerskog stajališta to je bio dizajn smeća. Ovu grešku sam primijetio tek nakon što sam snimio posljednje fotografije, ali sam prekinuo tu vezu, a zatim unosio izlaz OR gate -a u jedan od nekorištenih pretvarača iz logike upravljanja memorijom, a zatim spojio njegov izlaz na pin sata. Takođe sam popravio šemu i otkrio drugu grešku koju sam napravio. I ja sam to ispravio.

n

Nakon što je sve to konačno učinjeno, morao sam obaviti vrlo malu količinu posla: sklop za resetiranje. Dodao sam dugme na ploču i upotrijebio 10K otpornik da jednu stranu držim visoko. Druga strana ide direktno na tlo. Visoko podignuta strana je /RESET izlaz, koji je išao na svaki čip sa /RESET pinom (CPU i izlazna zasun). Da bih postigao resetiranje pri uključivanju, dodao sam kondenzator na /RESET izlaz. Ideja je da bi otpornik velike vrijednosti uzrokovao da se relativno veliki kondenzator sporo puni i zadrži pinove /RESET nisko za određenu količinu ciklusa takta (CPU -u su potrebna četiri ciklusa takta). Vjerovatno već možete pogoditi koja je negativna strana ovog kruga. Isti je negativ kao i prethodna verzija jer je to isto kolo. Kada se pritisne dugme, kondenzator se u suštini kratko spaja preko dugmeta. To je loše i za čep i za gumb, pa ako želite svoju građevinu učiniti trajnijom, možda ćete je htjeti redizajnirati. Razmišljao sam o drugom mjeraču vremena 555 postavljenom u monostabilnom načinu rada. Ali time je računarsko kolo sada završeno. Jej. Sada to treba programirati.

Korak 6: Programiranje

Programiranje ove stvari bilo je prava mora. Napravio sam Arduino EEPROM programer. Nije uspjelo. Napravio sam još jedan na osnovu tuđeg dizajna i kodiranja. I dalje nije funkcionisalo. Vratio sam se na iskušanu metodu ručnog postavljanja adresa i bajtova podataka ručno. Nekako sam to zabrljao. Pokušao sam ponovo i ipak sam pogriješio. Vratio sam se još jednom i otkrio da je isključen za jedan bajt, pa sam ga ispravio i konačno je uspjelo, hvala Bogu.

n

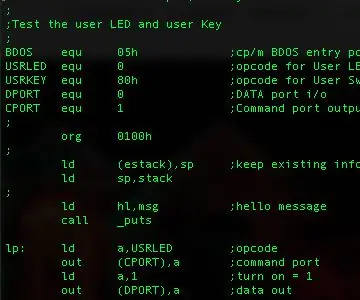

Što se tiče samog programa, izgleda da je super složen i teško ga je pratiti, ali nije. Zapravo je prilično jednostavno. Polovica toga prepisuje brojeve. Druga polovina se dijeli između 16-bitne matematike, uslovnih skokova i još više kopiranja brojeva. Pa da prođem kroz to i da vam kažem kako to funkcionira.

n

Inicijalizacija samo postavlja neke vrijednosti registra koje program koristi. Programska petlja je malo složenija, ali ne puno. Prvo prihvaća ulaz u A registar na portu 00. Zatim se E registar zapisuje u memoriju. U prve dvije petlje, E registar sadrži neželjene podatke, pa ih pokušavamo upisati u posljednja dva bajta ROM prostora jer se zapravo neće upisati; pokazivač adrese (IY) se zatim povećava. Vrijednost pohranjena u D se zatim premješta u E da bi se zatim upisala. A se zatim učitava u D i L i E kopira u H. HL je mjesto gdje se vrši usporedba vrijednosti oduzimanjem i provjerom ZF (nulta zastavica). Prva vrijednost u odnosu na pohranjena je u registre B i C. B i C se tretiraju kao jedan 16-bitni registar, BC. Ako su vrijednosti iste, program skače ravno u RAM prostor, gdje se pretpostavlja da se nalazi korisnički kod. Ako se kôd u BC -u ne podudara, tada se HL ponovo učitava s početnim vrijednostima iz D i E i ponovo se uspoređuje s vrijednošću u SP -u na isti način na koji je uspoređen s BC. Ako se podudara, ima isti rezultat, ali tri dodatna bajta se zapisuju u memoriju. Bajtovi su kod koji uzrokuje skok CPU -a na sam početak programa (resetiranje softvera). Međutim, ako se druga usporedba ne podudara, program se petlja do mjesta na kojem ugrabi vrijednost od korisnika.

n

LD SP, EDBFH; exe kod (dodaje skok)

n

LD IY, FFEH; početni pokazivač memorije za skladištenje koda

n

LD BC, EDC3H; exe kod (bez petlje)

n

petlja; asemblerska direktiva pa ne moramo znati gdje se u memoriji nalazi ovaj dio

n

U A, (00H); dobiti podatke o programu

n

LD (IY+00H), E; E sadrži kôd za pohranu

n

INC IY; prelazak na sljedeću memorijsku lokaciju

n

LD E, D; ld D u E

n

LD D, A; ld A u D

n

LD H, E; ld E u H

n

LD L, D; ld D u L

n

ILI A; resetirati zastavu za nošenje

n

SBC HL, BC; vraća 0 ako je unet exe kod 2

n

JP Z, 1000H; ako je tako, skočite na i izvršite program

n

LD H, E; u suprotnom ih osvježite na odgovarajuće vrijednosti

n

LD L, D

n

ILI A; prvi oduzimanje je možda postavilo zastavu za nošenje. Očisti to

n

SBC HL, SP; vraća 0 ako je unet exe kod 1

n

JP NZ, petlja; ako nije, ponovite postupak (počevši s dobivanjem vrijednosti)

n

LD (IY+00H), C3H; u suprotnom, unesite kod za preskakanje na kraju korisničkog programa

n

LD (IY+01H), 00H; jump u osnovi djeluje kao resetiranje softvera

n

LD (IY+02H), 00H; to je potpuno resetiranje u slučaju da su registri promijenjeni

n

JP 1000H; skočite na i izvršite korisnički program

Preporučuje se:

Z80-mbc2 Z80 Šifra blica LED za korisnika: 3 koraka

Z80-mbc2 Z80 Flash Flash LED za korisnike: Ovo je primjer korisničkog LED programa napisanog u Z80 asembleru za računar z80-mbc2. Ovo sam uradio za mene test i revizija, ovo je moj prvi program Z80 za više od 35 godina. Uživajte

Povratak u budućnost Antigravitacijski pad vode - Seeeduino Lotus: 5 koraka

Nazad u budućnost Antigravitacijska kap vode - Seeeduino Lotus: StoryTime je poput bujice koja gura ljude naprijed. Postoji li trenutak u kojem želite da stojite mirno ili se vratite unatrag? Pažljivo pogledajte kapljicu vode. Je li kapanje prema dolje ili prema gore? Djelo je inspirirano fenomenom vizualne perzij

3 ATtiny85 pinova Kontrola - Nrf24L01 - Povratak na vrh stranice: 7 koraka

3 ATtiny85 igle Kontrola - Nrf24L01 - التحكم بثلاثة دبابيس فى: بسم الله الرحمن الرحيم

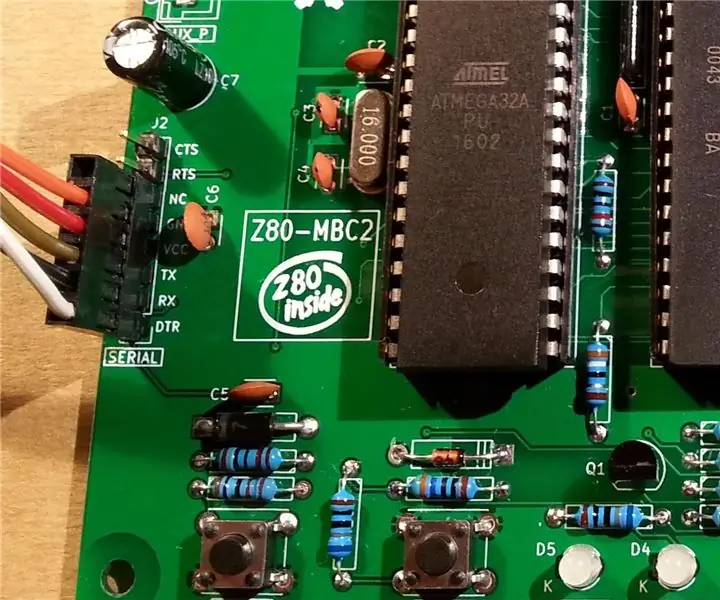

Pravi domaći računar koji se lako pravi: Z80-MBC2!: 9 koraka (sa slikama)

Pravi domaći računar koji se lako pravi: Z80-MBC2 !: Ako vas zanima kako računar radi i komunicira sa "vanjskim stvarima", danas postoji mnogo ploča spremnih za igru poput Arduina ili Raspberryja i mnogih drugih. Ali ove ploče imaju sve iste "limite" … zdravo

Sat za povratak u budućnost: 8 koraka (sa slikama)

Sat Povratak u budućnost: Ovaj projekat je započeo život kao budilica za mog sina. Učinio sam da izgleda kao vremenski krug od Povratak u budućnost. Zaslon može prikazati vrijeme u različitim formatima, uključujući onaj iz filmova, naravno. Može se konfigurirati pomoću tipki