Sadržaj:

- Korak 1: Postavljanje projekta u Vivadu za Ernie

- Korak 2: Kreiranje Ernijeve PWM u Vivadu

- Korak 3: Kreiranje Ernijevog TDOA -a u Vivadu

- Korak 4: Omotavanje i izvoz Ernie

- Korak 5: Izgradnja Ernieja

- Korak 6: Erniein prvi BSP

- Korak 7: FreeRTOS -ov Ernie

- Korak 8: Uvoz Ernijevog C koda

- Korak 9: Otklanjanje grešaka Ernie

- Korak 10: Učiniti Ernie autonomnom

- Korak 11: Učinite Ernie simpatičnom

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:05.

- Zadnja izmjena 2025-01-23 14:37.

Ovo je vodič o tome kako izgraditi Ernieja, vašeg autonomnog robota za praćenje zvuka, koristeći Zybo ploču. Obuhvatit će kako: stvoriti projekt u Vivadu, stvoriti upravljačke programe servo motora poput PWM-a u FPGA-i, sučelje s dva zvučna senzora, stvoriti vremensku razliku IP-a dolaska, koristiti freeRTOS i pokrenuti zybo iz baterije. Ovo je bio naš posljednji projekt za klasu operativnih sistema u stvarnom vremenu (CPE 439) na Cal Poly SLO.

Lista opreme:

- 1 - Razvojna ploča ZYBO Zynq 7000

- 2 - Servo paralelnog kontinuiranog okretanja

- 2 - Senzor zvuka (SparkFun detektor zvuka)

- 1 - 5v litijum -jonska USB baterija (za ploču)

- 4 - AA baterije (za servo pogone)

- 1 - AA baterija (sa 4 utora za baterije)

- 1 - Mikro USB kabl

- 1 - Oglasna ploča

- mnogo - muške do muške žice

- 1 - Servo kućište

Softverski zahtjevi:

- Xilinx Vivado Design Suite 2016.2

- Digilent Adept 2.16.1

Korak 1: Postavljanje projekta u Vivadu za Ernie

- Pojavit će se čarobnjak

- Pritisnite Dalje

-

Dajte sljedeći naziv projektu

- Nikada nemojte koristiti naziv projekta ili putanju direktorija koja ima razmake !!!!!

- Ovo će biti RTL projekat.

- Ne želimo navesti izvore

-

Klikom na Next dolazimo na stranicu Part. Koristimo ZYNQ XC7Z010-1CLG400C.

- Vivado nema Zybo naveden kao jednu od unaprijed definiranih ploča. Odaberite: “parts”, zatim potražite xc7z010clg400-1.

- Ako ste greškom odabrali pogrešan dio, lako možete promijeniti čipove: Alati -> Postavke projekta -> Općenito i kliknite točkice desno od "Projektni uređaj"

-

Kliknite Stvori dizajn bloka.

Dajte mu naziv design_1 za sada

- Vidjet ćete zelenu traku s natpisom Dodaj IP, kliknite na nju.

-

Potražite Zynq.

- Dvaput kliknite ZYNQ7 procesni sistem,

- Ovaj blok će se pojaviti u našem dizajnu bloka.

- Vidjet ćete zelenu traku na kojoj piše Run Block Automation, kliknite na nju.

- Preuzmite zybo_zynq_def.xml ispod.

-

U Vivadu kliknite "Uvezi XPS postavke" i odaberite "zybo_zynq_def.xml"

Ovo prethodno popunjava konfiguraciju bloka Vivado sa svim ugrađenim perifernim uređajima i dodjelom pinova Zybo ploče

-

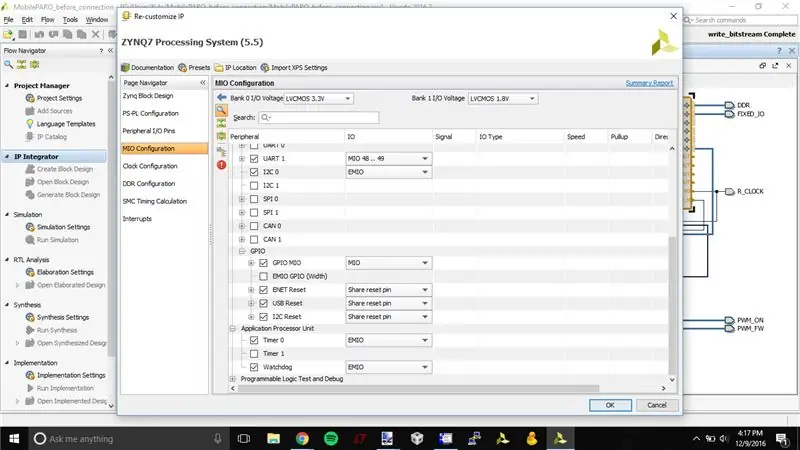

Dvaput kliknite na ZYNQ blok.

- MIO konfiguracija

- Omogući tajmer 0 (ispod jedinice procesorske aplikacije - img 1)

- Omogući Watchdog (pod jedinicom procesora aplikacije- img 1)

- Omogući GPIO-> GPIO MIO (u odjeljku Procesorska jedinica aplikacije - img 2)

- Omogući GPIO-> ENET Reset (ispod I/O periferije- img 2)

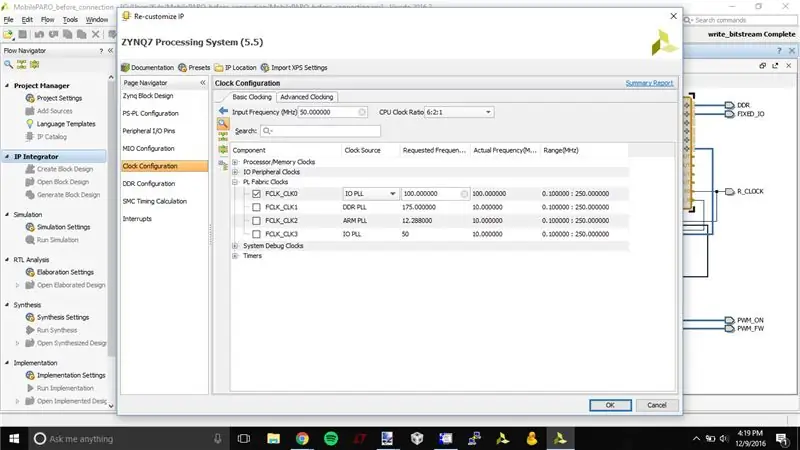

- Konfiguracija sata

Onemogućite FCLK0 (pod PL satovi od tkanine - img 3)

- MIO konfiguracija

- Pritisnite U redu.

-

“Pokreni automatizaciju blokova” sada.

Bit će nekih pitanja o signalima, recite OK

-

Kliknite na "Generiraj HDL omot".

Želimo kopirati generirani omot kako bismo omogućili korisnička uređivanja

- Pritisnite OK.

Korak 2: Kreiranje Ernijeve PWM u Vivadu

Ovaj korak će generirati PWM IP sa ulazima poslanim preko AXI biblioteke.

-

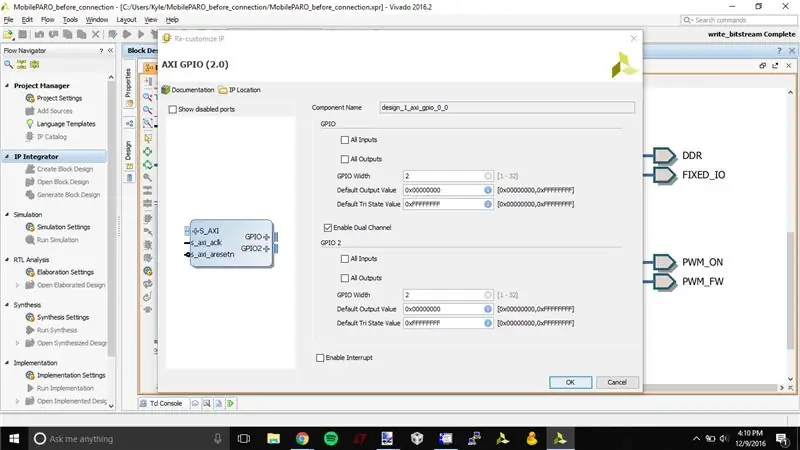

Napravite AXI GPIO blok desnim klikom na pozadinu i klikom na "dodaj IP"

upišite "AXI_GPIO" u traku za pretraživanje i odaberite ovaj paket

-

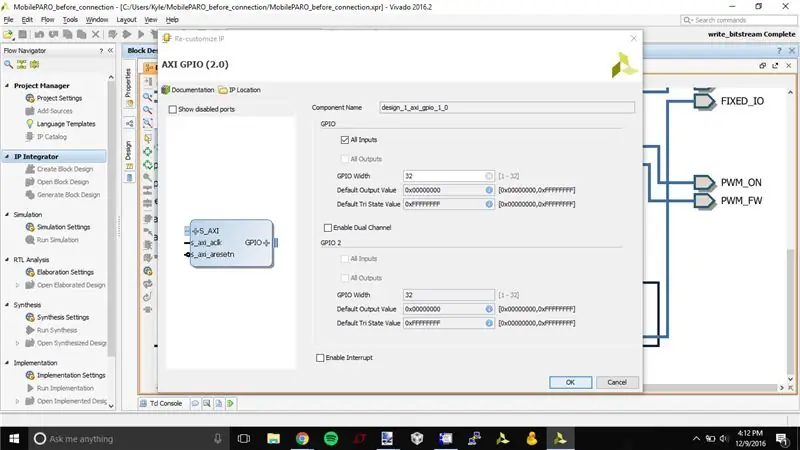

Ponovo prilagodite IP dvostrukim klikom na novi blok axi_gpio_0

- pod GPIO, postavite GPIO širinu na 2. Ovi bitovi će biti signal PWM_ON za pokretanje svake instance PWM modula.

- kliknite "omogući dvokanalni"

- pod GPIO 2, postavite GPIO širinu na 2. Ovi bitovi će biti signal PWM_FW za postavljanje smjera svake instance PWM modula.

-

Desnim klikom na izlazni port axi_gpio_0 s oznakom GPIO odaberite "Make External"

- Kliknite na novi izlaz s oznakom GPIO, idite na karticu "svojstva" na lijevoj alatnoj traci i promijenite naziv u PWM_ON

- Kliknite na novi izlaz s oznakom GPIO2, idite na karticu "svojstva" na lijevoj alatnoj traci i promijenite naziv u PWM_FW

-

Odaberite Pokreni automatizaciju veze na zelenom natpisu iznad blok dijagrama.

Ako ručno povežete portove, AXI adrese se možda neće konfigurirati, što kasnije dovodi do problema u komunikaciji

- U oknu Navigator protoka odaberite upravitelj projekta -> Dodaj izvore za stvaranje novog prilagođenog IP bloka

- odaberite "dodaj ili kreiraj izvore dizajna" i pritisni sljedeće

- kliknite "kreiraj datoteku", promijenite vrstu datoteke u "SystemVerilog" i upišite "pwm" u polje za naziv datoteke, a zatim kliknite u redu

- kliknite Završi

-

ignorirajte prozor Define Module pritiskom na OK (kasnije ćemo ih prepisati)

ako vas pita jeste li sigurni, kliknite Da

-

Na kartici izvori dvaput kliknite na pwm.sv (nalazi se u "Izvori dizajna/design_1_wrapper")

Kopirajte/zalijepite cijeli kôd SystemVerilog iz pwm.txt datoteke koja je dolje priložena

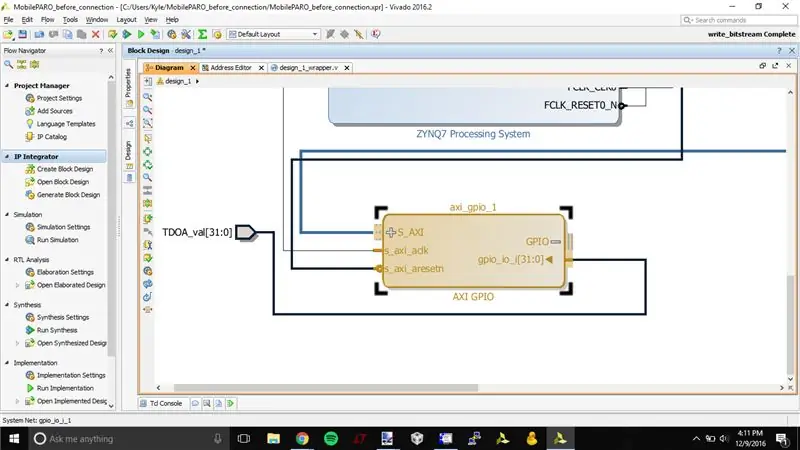

Korak 3: Kreiranje Ernijevog TDOA -a u Vivadu

Ovaj korak će generirati TDOA IP čiji se izlaz može čitati putem AXI biblioteke

-

Napravite AXI GPIO blok desnim klikom na pozadinu i klikom na "dodaj IP"

upišite "AXI_GPIO" u traku za pretraživanje i odaberite ovaj paket

-

Ponovo prilagodite IP dvostrukim klikom na novi axi_gpio_1 blok

- pod GPIO, označite polje "Svi ulazi" i postavite GPIO širinu na 32. Ova sabirnica će biti vremenska razlika dolaska između dva senzora.

- unutar axi_gpio_1 bloka, kliknite + pored GPIO porta da otkrijete gpio_io_i [31: 0].

-

Desnim klikom na izlazni port axi_gpio_1 označenim gpio_io_i [31: 0] odaberite "Make External"

Kliknite na novi unos označen gpio_io_i [31: 0], i idite do kartice "svojstva" na lijevoj traci s alatima i promijenite naziv u TDOA_val

-

Odaberite Pokreni automatizaciju veze na zelenom natpisu iznad blok dijagrama.

Ako ručno povežete portove, AXI adrese se možda neće konfigurirati, što kasnije dovodi do problema u komunikaciji

-

U oknu Navigator protoka odaberite upravitelj projekta -> Dodaj izvore da biste stvorili novi prilagođeni IP blok

- odaberite "dodaj ili kreiraj izvore dizajna" i pritisni sljedeće

- kliknite "kreiraj datoteku", promijenite vrstu datoteke u "SystemVerilog" i upišite "tdoa" u polje za naziv datoteke, a zatim kliknite u redu

- kliknite Završi

-

ignorirajte prozor Define Module pritiskom na OK (kasnije ćemo ih prepisati)

ako vas pita jeste li sigurni, kliknite Da

-

Na kartici izvori dvaput kliknite na tdoa.sv (nalazi se u "Izvori dizajna/design_1_wrapper")

Kopirajte/zalijepite cijeli kôd SystemVerilog iz donje priložene datoteke tdoa.txt

Korak 4: Omotavanje i izvoz Ernie

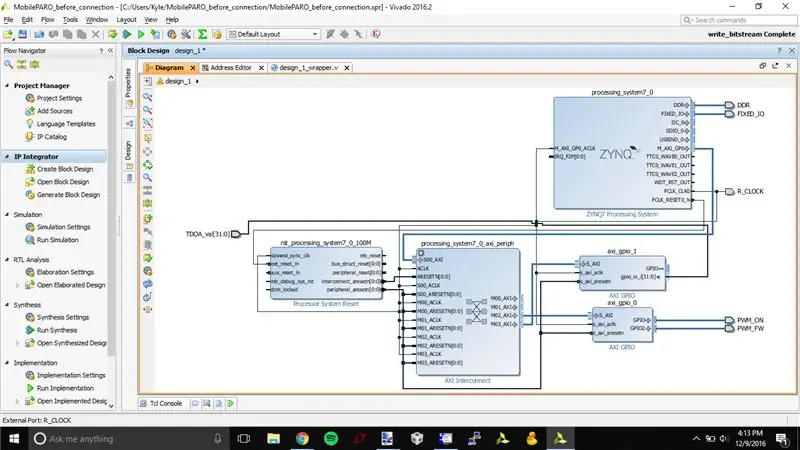

- Provjerite izgleda li blok dijagram kao priloženi snimak zaslona

-

Na kartici izvori kliknite desnom tipkom miša design_1.bd i odaberite "Create HDL Wrapper …"

- Odaberite "Kopiraj generirani izlaz za dopuštanje korisničkih uređivanja", a zatim pritisnite "OK"

- Kopirajte kôd iz design_1_wrapper.txt dolje priloženog i zalijepite ga umjesto generiranog code_1_wrapper.v koda

- spremi design_1_wrapper.v

-

Na kartici izvori dvaput kliknite na datoteku ZYBO_Master.xdc u okviru Ograničenja/constrs1

- Kopirajte kôd iz dolje priloženog ZYBO_Master.txt -a i zalijepite ga umjesto postojećeg ZYBO_Master.xdc koda

-

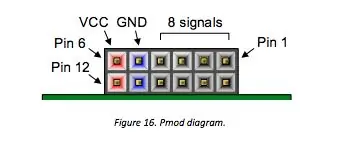

Obratite pažnju na sljedeće ulazno/izlazne pinove:

- L15: PWM signal za lijevi motor (Pmod JA2 na Zybo -u)

- L14: PWM signal za desni motor (Pmod JA8 na Zybo -u)

- V12: ulaz kapije sa senzora zvuka 1 (Pmod JE1 na Zybo -u)

- K16: ulaz kapije sa senzora zvuka 2 (Pmod JE2 na Zybo -u)

- U oknu Navigator protoka kliknite "Generiraj bitstream" u odjeljku Program i otklanjanje grešaka

ako mislite da je to odmah učinjeno, vjerojatno nije. ozbiljno, skuhaj čaj

-

Kliknite Datoteka-> Izvoz-> Generiraj hardver

Označite "Uključi Bitstream" i pritisnite OK

- Kliknite Datoteka-> Pokreni SDK

Korak 5: Izgradnja Ernieja

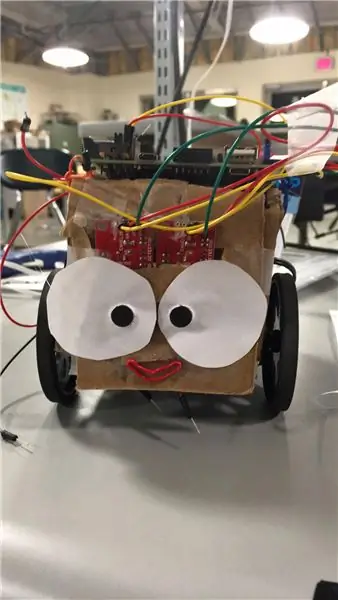

- Montirajte servo pogone na servo kućište.

-

Prateći tehnički list za servo pogone, učinite sljedeće:

- spojite uzemljenje servo pogona na uzemljenje na Zybo -ovom JA Pmod -u (pogledajte priloženu sliku iscrtavanja)

-

spojite pin za napajanje servo -a na AA bateriju

Otkrili smo da kada su servo upravljači spojeni na Zybo -ov Vdd, ploča crpi previše struje, uzrokujući neprestano resetiranje ploče

- priključite pinove ulaznog signala na odgovarajuće izlazne pinove Zybo -a (lijevo: JA2, desno: JA8)

- montirajte senzore zvuka na prednju stranu kućišta, okrenutu prema naprijed, držeći ih što bliže moguće

- upotrijebite vodič za povezivanje senzora zvuka za integraciju senzora zvuka

- ožičite uzemljenje i Vdd pinove svakog senzora zvuka sa uzemljenjem i Vdd pinove na Zybo -ovom JE Pmod -u (pogledajte priloženu sliku pinout -a)

- spojite iglu kapije lijevog senzora zvuka na JE1

- spojite pin vrata desnog senzora zvuka na JE2

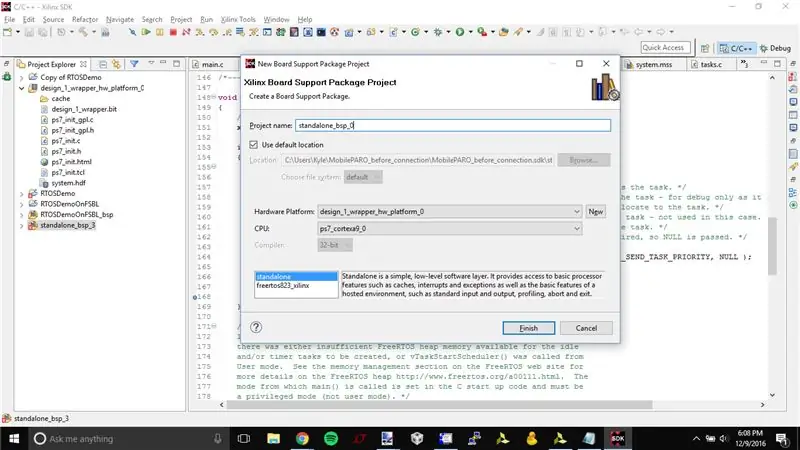

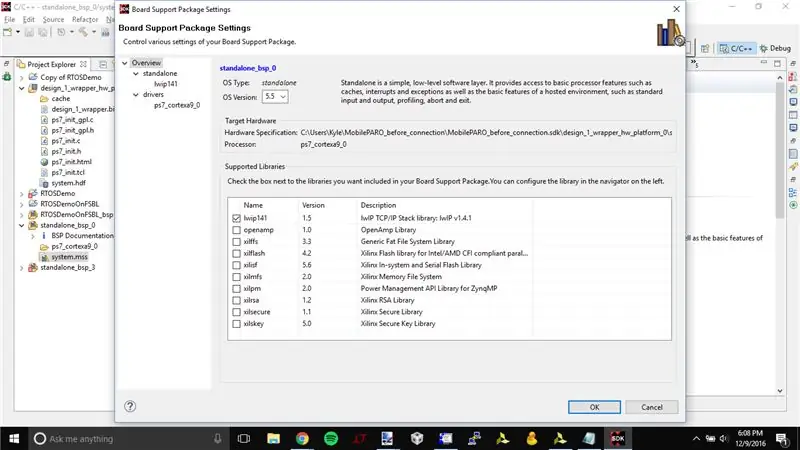

Korak 6: Erniein prvi BSP

-

Napravite BSP za zaključivanje platforme koju smo upravo stvorili.

To možete dobiti putem File -> New -> Board Support Package

-

Pojavit će se čarobnjak koji će vam pomoći u stvaranju BSP -a.

- Želimo povezati ovaj BSP s našom platformom koju smo upravo stvorili, pa

- Hardverska platforma bi trebala biti u skladu s onom koju smo upravo stvorili (vidi img 1)

- Naš CPU će biti _0 CPU.

- Pritisnite Finish

- Obavezno provjerite da li lwip141 sadrži vaš bsp u prozoru koji se pojavi (pogledajte sliku 2)

Korak 7: FreeRTOS -ov Ernie

-

Preuzmite najnovije izdanje FreeRTOS -a sa Sourceforge -a.

Ako je preuzimanje izvršna datoteka, pokrenite je da biste ekstrahirali datoteke FreeRTOS u direktorij vašeg projekta

- Držite SDK otvoren i kliknite Datoteka -> Uvoz.

- Želimo kliknuti Općenito-> Iz postojećeg radnog prostora, a zatim ćemo htjeti otići do mjesta gdje smo preuzeli FreeRTOS.

-

Naš demo će se nalaziti u FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702. Odabirom ove mape trebali bismo vidjeti tri projekta (naš kod (OS), to je BSP i HW platforma).

SAMO Uvezite RTOSDemo u vaš trenutni radni prostor

-

Na svim projektima „plavih“foldera promijenite referentni BSP

- Desnim klikom i odabirom "Promijeni referentni BSP".

- Odaberite BSP koji ste upravo stvorili za svoj Zybo

- Uređivanje koda u Xilinxovim SDK plavim mapama su stvarni projekti koda.

Korak 8: Uvoz Ernijevog C koda

- U direktoriju RTOSDemo/src prepišite postojeći main.c sa datotekom main.c koja je ovde priložena.

- Kopirajte datoteku main_sound.c u direktorij RTOSDemo/src.

Korak 9: Otklanjanje grešaka Ernie

- Odaberite Run -> Debug Configurations

- U lijevom oknu kreirajte novi pokretač programa System Debugger

-

Na kartici Target Setup,

odaberite „Resetiraj cijeli sistem“tako da se odaberu i taj i ps7_init

-

Sada odaberite karticu Aplikacija.

- Odaberite "Preuzmi aplikaciju"

- Postavite jezgru cortexa9_0 na "zaustavi se pri ulasku u program"

- Pritisnite Apply and Debug.

- Proverite da nema grešaka u procesu otklanjanja grešaka

- Pažljivo nadgledajući robota, pritisnite dugme Nastavi dok se program ne pokrene bez pogađanja tačaka prekida

- Robot bi se sada trebao okrenuti i krenuti prema jakim zvukovima. Jej!

Korak 10: Učiniti Ernie autonomnom

- Kada vaš projekt bude spreman za rad (možete bez problema pokrenuti program za otklanjanje grešaka), spremni ste za učitavanje u flash memoriju na ploči.

-

Kreirajte ono što se naziva “first stage boot loader” (FSBL) projekt i sadrži sve upute koje će vašoj ploči biti potrebne za učitavanje vaših projektnih datoteka (bit bit i OS) pri pokretanju.

- Odaberite: File-> New-> Application Project i trebao bi se pojaviti sljedeći prozor.

- Dajte mu ime kako želite (tj. "FSBL")

- Uvjerite se da je hardverska platforma ta s kojom radite

- Pritisnite sljedeći (Ne pritisnite Završi)

- Odaberite predložak Zynq FSBL

- Kliknite završi.

- Kada proces kreiranja bude dovršen, znat ćete je li sve funkcioniralo ako vidite sljedeće dvije nove mape u prozoru Project Explorer.

-

Kreirajte sliku za pokretanje Sada ćete morati stvoriti sliku za pokretanje.

- Desnim klikom na fasciklu vašeg projekta (u ovom slučaju moja se zove “RTOSDemo”)

- Na padajućem izborniku kliknite "Kreiraj sliku za pokretanje"

-

Ako je sve ispravno povezano, projekt će znati koje datoteke mu trebaju i sljedeći prozor će izgledati kao što vidite dolje (ključno je da imate 3 particije u odjeljku Boot image, pokretački program, vašu bit datoteku i.elf datoteku vaših projekata).).

Ako to nije slučaj, moguće je da nešto nije u redu s povezivanjem vašeg projekta. Osigurajte da su fascikle projekta povezane sa odgovarajućim BSP -ovima

- Kliknite na dugme „Kreiraj sliku“

-

Posljednji korak u softveru je sada premjestiti prethodno stvorenu sliku u memoriju ploče

- Odaberite s glavne SDK trake s alatima odaberite Xilinx Tools-> Program Flash Memory

- Uvjerite se da je odabrana ispravna hardverska platforma i da putanja datoteke slike ispravno upućuje na. BIN datoteku stvorenu u prethodnom koraku.

- Odaberite „qspi single“iz vrste Flash

- Označite “Verify after flash” kako biste osigurali integritet, ali to nije potrebno

- Konfigurirajte svoju ploču Na kraju morate osigurati da je kratkospojnik za način programiranja ploča (JP5) ispravno postavljen za odabir pokretanja s qspi -a (koji sadrži ono što ste upravo bljeskali) kada se pokrene BootROM.

- Sada jednostavno uključite uređaj i uključite uređaj i osigurajte da LED lampica “Logic Configuration Done” (LED 10) svijetli zeleno.

Korak 11: Učinite Ernie simpatičnom

- Krzno

- Puno krzna

- Velike oči!

- … Kapa

Preporučuje se:

Uradi sam Kako napraviti sat koji izgleda lijepo - StickC - Jednostavno za napraviti: 8 koraka

Uradi sam Kako napraviti sat sa lijepim izgledom - StickC - Lako za napraviti: U ovom ćemo vodiču naučiti kako programirati ESP32 M5Stack StickC s Arduino IDE -om i Visuinom za prikaz vremena na LCD -u te također podesiti vrijeme pomoću tipki StickC

Kako napraviti brojač koraka?: 3 koraka (sa slikama)

Kako napraviti brojač koraka?: Nekada sam se dobro snašao u mnogim sportovima: hodanje, trčanje, vožnja bicikla, igranje badmintona itd. Volim jahanje da bih brzo putovao. Pa, pogledaj moj trbušni trbuh … Pa, u svakom slučaju, odlučujem ponovo početi vježbati. Koju opremu treba pripremiti?

KAKO NAPRAVITI ARDUINO NANO/MINI - Kako snimiti bootloader: 5 koraka

KAKO NAPRAVITI ARDUINO NANO/MINI | Kako snimiti Bootloader: U ovom uputstvu ću vam pokazati kako napraviti Arduino MINI od ogrebotina. Postupak napisan u ovim uputama može se koristiti za izradu bilo koje arduino ploče za vaše prilagođene zahtjeve projekta. Molimo vas da pogledate video za bolje razumijevanje

Kako napraviti zamka za vrata kako biste zaštitili svoju bazu !!!: 6 koraka

Kako napraviti zamka za vrata kako biste zaštitili svoju bazu !!!: Danas smo htjeli naučiti kako napraviti sjajna vrata za zaštitu od baze

Kako napraviti kalendar djeda i baka & Spomenar (čak i ako ne znate kako napraviti spomenar): 8 koraka (sa slikama)

Kako napraviti kalendar djeda i baka & Spomenar (čak i ako ne znate kako se bilježiti): Ovo je vrlo ekonomičan (i cijenjen!) Praznični poklon za bake i djedove. Ove sam godine napravio 5 kalendara za manje od 7 dolara svaki. Materijali: 12 sjajnih fotografija vašeg djeteta, djece, nećaka, nećaka, pasa, mačaka ili druge rodbine12 različitih komada