Sadržaj:

- Korak 1: Blok dijagram

- Korak 2: Princip rada

- Korak 3: Implementacija logike

- Korak 4: Rješavanje zastoja

- Korak 5: Konfiguracija uređaja - Matrix0 krug

- Korak 6: Konfiguracija uređaja - SPI logika taktiranja

- Korak 7: Konfiguracija uređaja - Svojstva komponenti Matrix0

- Korak 8: Konfiguracija uređaja - Matrix1 krug

- Korak 9: Konfiguracija uređaja - 3 -bitni binarni brojač

- Korak 10: Konfiguracija uređaja - 3 -bitna logika usporedbe

- Korak 11: Konfiguracija uređaja - Logika digitalnog poređenja i privremeni registar

- Korak 12: Konfiguracija uređaja - Svojstva komponenti Matrix1

- Korak 13: Rezultati

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:05.

- Zadnja izmjena 2025-01-23 14:37.

Upravljački sistemi i povezani uređaji bave se višestrukim izvorima napajanja, poput vodova za prednapon ili baterijama, i moraju pratiti najvišu (ili najnižu) liniju u danom skupu.

Na primjer, prebacivanje opterećenja u sustavu na "više baterija" zahtijeva da sistem nadgleda ili minimalni ili maksimalni napon među nizom baterija (max ili min u zavisnosti od određenog algoritma prebacivanja) i dinamički usmjerava opterećenje na najprikladniji izvor u realnom vremenu. Alternativno, sustav će možda morati privremeno isključiti akumulator najnižeg napona radi pravilnog punjenja.

Drugi primjer je savremeni solarni sistem za napajanje, gdje je svaka solarna ploča opremljena mehanizmom za naginjanje i solarnim krugom za praćenje (potonji daje informacije o položaju Sunca za orijentaciju panela). Uz podatke o maksimalnom naponu, svaki položaj solarnog panela može se fino podesiti na osnovu panela niza koji zapravo daje najveći izlazni napon, čime se postiže vrhunski nivo optimizacije snage.

Postoji nekoliko različitih marki komercijalnih IC -ova (uglavnom mikrokontrolera) koji u načelu mogu implementirati sljedbenik maksimalnog napona. Međutim, zahtijevaju programiranje i manje su isplativi od rješenja s mješovitim signalom. Dopuna Dialog GreenPAKTM dizajna može pozitivno utjecati na pristupačnost, veličinu i modularnost dizajna. Ovaj dizajn koristi prednosti integracije analognih i digitalnih kola u jedan čip.

U ovom Instructable-u je implementiran analogni prednji kraj i digitalna logika potrebna za implementaciju uređaja za pronalaženje maksimalnog (ili eventualno minimalnog) napona među osam različitih izvora.

Za implementaciju 8-kanalnog analognog monitora maksimalnog/min napona koristi se SLG46620G.

U nastavku smo opisali korake potrebne za razumijevanje načina na koji je rješenje programirano za stvaranje 8-kanalnog analognog monitora maksimalnog/min napona. Međutim, ako samo želite dobiti rezultat programiranja, preuzmite GreenPAK softver da biste vidjeli već završenu GreenPAK datoteku za dizajn. Priključite GreenPAK Development Kit na svoje računalo i hit program za stvaranje 8-kanalnog analognog monitora maksimalnog/min napona.

Korak 1: Blok dijagram

Na slici 1 prikazan je globalni dijagram implementiranog sistema.

Niz do 8 izvora promjenjivog napona je multipleksiran i povezan s GreenPAK -ovim ADC modulom povezanim prema prilagođenom internom dizajnu sposobnom za odabir izvora s najvećim naponom u odnosu na ostale. Interna logika šalje ove informacije za prikaz ili daljnju obradu.

Dizajn se temelji na proizvodu GreenPAK SLG46620G, jer ugrađuje sve potrebne analogne i digitalne građevne blokove za aplikaciju. U ovoj implementaciji niz se skenira pomoću ADG508 analognog multipleksera koji direktno pokreće GreenPAK IC.

Izlazna informacija je 3-bitni digitalni broj koji odgovara broju izvora napona pri maksimalnom naponu. Direktan način da dođete do ovih informacija je da prikažete broj pomoću 7-segmentnog ekrana. To se može lako postići povezivanjem digitalnog izlaza SLG46620G sa 7-segmentnim upravljačkim programom za prikaz, kao što je rješenje GreenPAK opisano u Reference ili sa uobičajenim IC-om 74LS47.

Predstavljeno kolo traži maksimalni napon. Za pretvaranje dizajna u uređaj za pronalaženje minimalnog napona, potrebno je dodati jednostavno kolo predkondicioniranja između analognog multipleksera i GreenPAK analognog ulaza, oduzimajući izlaz multipleksera od referentnog napona od 1 V.

Korak 2: Princip rada

Dizajn ima za cilj odabir izvora s maksimalnim naponom, pa se skeniranje vrši na cijelom nizu uz pohranu posljednje maksimalne vrijednosti i usporedbu sa sljedećom vrijednošću na ulazu (koja pripada sljedećem izvoru napona u skeniranju).

U nastavku ćemo se pozivati na kompletan niz multipleksiranja duž svih ulaza kao „skeniranje“ili „petlja“.

Poređenje između dvije vrijednosti ne postiže se pomoću komponenti ACMP (međutim, dostupnih u SLG46620G), već pomoću DCMP modula, nakon što se vrijednosti digitaliziraju. Ovo je napredna i rafinirana tehnika koja je prvi put obrađena u Referenci.

Slika 2 prikazuje kako je SLG46620G strukturiran za ovaj dizajn.

Analogni ulazni signal ide na ADC ulaz kroz PGA komponentu sa postavljenim pojačanjem 1. Različite postavke pojačanja su također moguće pronaći najbolje usklađivanje sa elektronikom kondicioniranja na prednjem kraju namijenjenom preslikavanju ulaznih napona na 0-1 V raspon GreenPAK ADC modula.

ADC radi u neograničenom načinu rada i pretvara analogni signal u 8-bitni digitalni kod, koji se zatim prenosi u DCMP modul. Digitalni kod se također unosi u SPI blok, konfiguriran kao ADC/FSM međuspremnik, gdje se digitalni kod može pohraniti i neće se mijenjati dok sljedeći impuls ne dođe na ulaz SPI CLK. Primijetite da namjenski logički blok pokreće SPI CLK ulaz. Kasnije ćemo istražiti ovaj dio jer je to "jezgra" logika odgovorna za pravilan rad. Novi digitalni kôd sprema se u SPI modul samo ako pripada stvarnom maksimalnom ulaznom naponu.

DCMP komponenta se koristi za upoređivanje trenutnih ADC podataka sa posljednjim pobjednikom (to je posljednji pronađeni maksimum) koji je pohranjen u SPI bloku. On će generirati impuls na OUT+ izlazu kada su novi ADC podaci veći od prethodnih. Koristimo OUT+ signal za ažuriranje SPI bloka s novim pobjednikom.

Globalni signal sata pokreće ADC konverzije i općenito vrijeme. Nakon što se konverzija izvrši, izlazni signal ADC -ovog INT izlaznog impulsa, vremenski usklađen s ADC paralelnim izlazom podataka. INT izlaz koristimo i za povećanje 3-bitnog binarnog brojača, implementiranog od DFF-ova u Matrix1, što je korisno iz tri razloga:

1. Izlazne linije brojača obraćaju se vanjskom analognom multiplekseru, čime opslužuju sljedeći ulazni napon ADC -a;

2. Brojanje je zamrznuto u 3-bitni registar (implementirano u Matrix1) za pohranu privremenog pobjednika tokom skeniranja;

3. Brojanje se dekodira za ažuriranje drugog 3-bitnog registra (implementirano u Matrix0) nakon što se skeniranje završi.

Korak 3: Implementacija logike

ADC modul uzastopno pruža konvertirane podatke svih ulaznih napona, jedan za drugim, neograničeno dugo. Jednom kada se multiplekseru adresira 0b111 (decimal 7), brojač se otkotrlja na 0b000 (decimal 0) čime započinje novo skeniranje ulaznih napona.

Tokom skeniranja, izlazni signal ADC INT -a generiše se kada je paralelan izlaz podataka ispravan. Kada ovaj signal pulsira, analogni multiplekser mora preći na sljedeći ulaz, dajući PGA -u odgovarajući napon. Stoga je izlaz ADC INT izravni signal taktiranja 3-bitnog binarnog brojača sa slike 2, čija 3-bitna paralelna izlazna riječ izravno obraća vanjski analogni multiplekser (“V select” na slici 1).

Pogledajmo sada primjer gdje bi ulazni naponi trebali imati sljedeće odnose:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Slika 3 predstavlja glavne signale uključene u mehanizam maksimalne odluke.

Budući da se podaci na kraju spremaju u SPI bafer -registar sinhrono s INT impulsima, postoji prozor za usporedbu gdje se sadržaj SPI bafera uspoređuje sa sljedećim rezultatom konverzije ADC -a. Ovo određeno vrijeme rezultira generiranjem OUT+ impulsa na DCMP izlazu. Ove impulse možemo iskoristiti za učitavanje novih vrijednosti u SPI bafer -registar.

Kao što je vidljivo iz linije podataka međuspremnika SPI prethodne slike, SPI registar uvijek sadrži najveću vrijednost među 8 ulaza i ažurira se samo kada DCMP modul otkrije veću vrijednost (odnosi se na DCMP OUT+ izlazna linija grafikona, nedostajući impulsi uzrokuju da V2 ostane blokiran u registru sve dok se ne usporedi s V5).

Korak 4: Rješavanje zastoja

Kada bi implementirana logika bila baš onako kako je gore opisano, jasno je da bismo naišli na zastoj: sistem je sposoban otkriti samo napone veće od onog koji odgovara onome što je pohranjeno u SPI bafer registru.

Ovo vrijedi i u slučaju da bi se ovaj napon smanjio, a zatim bi drugi ulaz, do sada manji od toga, postao najveći: nikada se ne bi otkrio. Ova situacija je bolje objašnjena na slici 4, gdje su prisutna samo 3 ulazna napona jasnoća.

U vrijeme ponavljanja 2, V3 opada, a V1 je stvarni maksimalni napon. No, DCMP modul ne daje impuls jer su podaci pohranjeni u registru međuspremnika SPI (što odgovara 0,6 V) veći od podataka koji odgovaraju V1 (0,4 V).

Sistem se tada ponaša kao "apsolutni" tragač za maksimum i ne ažurira ispravno izlaz.

Lijep način za prevladavanje ovog problema je prisilno učitavanje podataka u SPI bafer registar kada sistem završi cijeli ciklus prozivanja svih kanala.

U stvari, ako je napon na tom ulazu i dalje najveći, ništa se ne mijenja i kontrola se sigurno nastavlja (pozivajući se na gornju sliku 4, ovo je slučaj petlji Iteracija 0 i 1). S druge strane, ako se napon na tom ulazu slučajno spusti na vrijednost manju od drugog ulaza, ponovno učitavanje vrijednosti daje mogućnost DCMP modulu da proizvede OUT+ impuls kada ga uporedi s novom maksimalnom vrijednošću (to je slučaj petlje Iteracije 2 i 3).

Dio logičkog kruga je neophodan da bi se prevladao problem. On mora generirati signal sata prema SPI komponenti kada petlja dosegne stvarni maksimalni ulaz, čime se forsira ponovno učitavanje ažurirane riječi podataka u SPI bafer registar. O tome će biti riječi u odjeljcima 7.2 i 7.6 u nastavku.

Korak 5: Konfiguracija uređaja - Matrix0 krug

SLG46620G ima dva matrična bloka, kao što je prikazano na slici 2. Sljedeće slike prikazuju odgovarajuće konfiguracije uređaja.

Gornji dio kola je “Loop Register” realiziran sa 3 DFF -a (DFF0, DFF1 i DFF2). Osvježava se nakon svake petlje ulaznog multipleksera kako bi 7-segmentnom upravljačkom programu ekrana poslao binarni broj “pobjednika”, to jest ulaza s najvećim naponom u posljednjem skeniranju. Takt DFF -ova i podaci dolaze iz logike implementirane u Matrix1 preko porta P12, P13, P14 i P15.

Donji dio je analogni prednji kraj sa ulazom na Pin 8 i PGA sa pojačanjem x1. Izlaz ADC INT ide i na logiku taktiranja SPI -a i na Matrix1 preko porta P0, gdje će poslužiti kao signal sata za implementirani brojač.

Paralelni izlazi podataka ADC i SPI imaju oznake NET11 i NET15 za povezivanje sa DCMP komponentom u Matrix1.

Korak 6: Konfiguracija uređaja - SPI logika taktiranja

Kao što je ranije istaknuto u odjeljku „Implementacija logike“, SPI međuspremnik se ažurira svaki put kada usporedba između stvarne pohranjene vrijednosti i novih ADC konverzijskih podataka generira impuls na izlazu DCMP OUT+.

Integritet signala je osiguran ako je ovaj signal AND-ed sa izlazom ADC INT. Time se izbjegava bilo kakav skok i lažno aktiviranje.

Također smo podcrtali da se za preskakanje zastoja SPI međuspremnik mora ažurirati kada petlja dođe do stvarnih podataka pobjednika.

U igri su tada tri signala za pravilno SPI taktiranje:

1. ADC INT izlaz (LUT0-IN1)

2. DCMP OUT+ izlaz (LUT0-IN0 preko porta P10)

3. Brojanje je jednako signalu zasuna (LUT0-IN2 preko priključka P11)

Prva dva su AND-ed i oba OR-ed sa posljednjim u LUT0, čija je implementacija konfigurirana kao na slici 6.

Korak 7: Konfiguracija uređaja - Svojstva komponenti Matrix0

Slike 7-10 prikazuju preostale prozore svojstava komponenti koji pripadaju Matrix0.

Korak 8: Konfiguracija uređaja - Matrix1 krug

Korak 9: Konfiguracija uređaja - 3 -bitni binarni brojač

Gornji dio kola sadrži logičke elemente, uglavnom 3-bitni binarni brojač koji radi na ADC INT izlazu, kako je već rečeno. Ovaj brojač je implementiran sa sasvim „standardnom“shemom prikazanom na slici 12.

Ovaj brojač je u našem dizajnu realiziran pomoću japanki DFF9, DFF10, DFF11 i INV1, LUT4, LUT8. Izlaz DFF9 je LSB, dok je DFF11 MSB, kao što je prikazano na slici 13.

LUT4 je konfiguriran kao XOR, dok LUT8 izvodi logiku AND-XOR sa slike 12.

Brojački izlazi idu na tri digitalna izlaza za adresiranje vanjskog analognog multipleksera.

LUT10 dekodira kod brojača kada je skeniranje završeno i šalje impuls u Matrix0 putem DLY8 i porta P12. Ovo se jednostavno postiže AND-in izlazom brojača, dekodirajući tako broj 7 dec (0b111 binarno, kraj petlje).

Korak 10: Konfiguracija uređaja - 3 -bitna logika usporedbe

Slika 15 prikazuje krug koji se koristi za otkrivanje kada petlja iterira na trenutnoj “pobjedničkoj” adresi. U ovom slučaju, kao što je već rečeno, digitalni impuls trebao bi prisiliti ponovno učitavanje trenutnog rezultata ADC-a kako bi se riješila moguća situacija zastoja.

Adresa „pobjednika“pohranjena je u privremenom registru Matrix1 (vidi dolje), dok se trenutna adresa prikazuje binarnim brojačem.

XNOR kapije pružaju pravi (logički 1 ili 'visoki') izlaz kada su oba ulaza jednaka. I-ovaj signal za sve bitove (LUT9) daje nam puls kada su oba binarna koda ista. Pojedinosti o XOR vratima kao provjeri pariteta mogu se pronaći u Reference.

Signal „Counter-equals-Latch“se prenosi u Matrix0 preko porta P11.

Korak 11: Konfiguracija uređaja - Logika digitalnog poređenja i privremeni registar

Donji dio slike 11 (istaknut na slici 16) prikazuje DCMP blok, dio odlučivanja u ovom dizajnu.

DFF6, 7 i 8 formiraju 3-bitni registar za pohranu privremenog ulaznog broja "pobjednik" dok je petlja u toku. Ulazi u japanke su 3-bitni binarni izlazi brojača, što je vidljivo u globalnom krugu Matrix1 na slici 11, ovdje preskočeni radi jasnoće.

Izlazi ovog registra ne mogu pokretati izravno 7-segmentni zaslon jer se ovdje pohranjena vrijednost mijenja tokom skeniranja i treba ih smatrati "valjanima" samo na kraju samog skeniranja.

Iz tog razloga, izlazi privremenog registra povezuju se s Loop registrom Matrix0 preko među matričnih portova P13, P14 i P15.

Važno je primijetiti na slici 16 da privremeni registar blokira izlaz DCMP OUT+ kada ADC-SPI registrira rezultate usporedbe u novom nađenom maksimumu.

Isti OUT+ signal se prenosi na Matrix0, SPI CLK Logic, preko porta P10.

Korak 12: Konfiguracija uređaja - Svojstva komponenti Matrix1

Slike 17-19 prikazuju prozore svojstava komponenti koji pripadaju Matrix1.

Korak 13: Rezultati

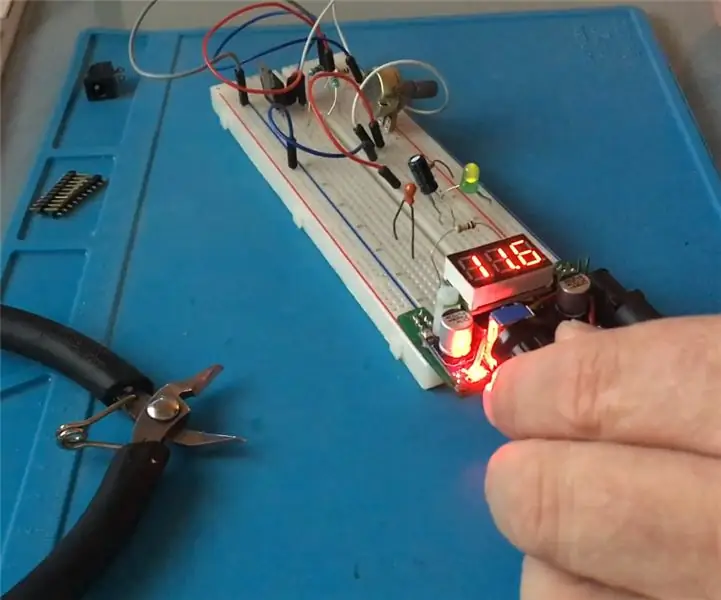

Kako bi se testirala implementacija, konstruiran je prototip ploče za procjenu, gdje se 8 analognih ulaznih napona dobiva nizom otporničkih razdjelnika s TrimPots -om (kao što je prikazano na slici 20).

Korišteni multiplekser je ADG508, dio koji može raditi s jednim napajanjem (12 V).

Upravljački program za 7-segmentni ekran je 74LS47. Dekodira paralelnu ulaznu riječ i direktno pokreće 7-segmentni ekran sa zajedničkom anodom.

Ploča za procjenu ima 2x10 pravokutni konektor za direktno priključivanje na GreenPAK naprednu razvojnu platformu na svom priključku za proširenje, kao što je prikazano na slici 21.

U kombinaciji s GreenPAK naprednom razvojnom platformom čini vrlo jednostavnim mjerenje signala za brzu provjeru. Na primjer, slika 22 prikazuje skup signala (odnosno CLOCK, ADC INT izlaz i DCMP OUT+ izlaz) snimljene pomoću HP 54620A logičkog analizatora. Oblici talasa pokreću se rastućom ivicom OUT+ signala (u opsegu označenom s 'A> B'), stoga je ovo hvatanje valnog oblika kada se među analognim ulazima detektira novi maksimalni napon. Zapravo, dobiveno je rotiranjem jednog od trimpotova evaluacijske ploče kako bi se povećao odgovarajući napon prikazan na slici 22.

Slika 23 prikazuje shemu Odbora za ocjenjivanje.

Zaključak

U ovom Instructable-u implementirali smo osmokanalni maksimalni (ili minimalni) napon koji se koristi kao uobičajeni dodatak višekanalnim upravljačkim sistemima. Predstavljeni pristup koristi napredne karakteristike GreenPAK komponenti i pokazuje kako je moguće integrirati u jedan čip analogne i digitalne funkcije. Nekoliko komercijalnih IC -a može se zamijeniti Dialog GreenPAK -ovima kako bi se smanjila veličina i cijena aplikacije.

Preporučuje se:

Mjerač istosmjernog napona u džepu veličine "uradi sam": 5 koraka

DIY mjerač DC napona veličine džepa: U ovom uputstvu ću vam pokazati kako sami napraviti džepni mjerač istosmjernog napona veličine džepa sa piezo zujalicom za provjeru kola. Sve što vam treba je osnovno znanje o elektronici i malo vremena. Ako imate bilo kakvih pitanja ili problema, možete

Uradi sam lični monitor vremenske stanice: 6 koraka

DIY Personal Weather Station Monitor: DarkSky ,, Naša API usluga za postojeće korisnike danas se ne mijenja, ali više nećemo prihvaćati nove registracije. API će nastaviti funkcionirati do kraja 2021. https: //blog.darksky.net/Osobni monitor vremenske stanice prikazuje vaš mi

Uradi sam Uradi BB-8 u Indiji -- Android kontroliran i pričljiv -- U prirodnoj veličini: 19 koraka (sa slikama)

Uradi sam Uradi BB-8 u Indiji || Android kontroliran i pričljiv || U prirodnoj veličini: PRETPLATITE SE na moj kanal za više projekata. Ovaj projekt govori o tome kako izgraditi radni, pričajući, pričajući, drvar Starwars BB-8 kontroliran arduinom. koristit ćemo samo kućanske materijale i malo Arduino sklopova. U ovome smo

Regulator napona na ploči s zaslonom / Regulatorom napona Com displejom Za sve potrebne postavke: 8 koraka

Regulator napona na ploči s zaslonom / Regulator napona Com zaslon Para Placa De Ensaio: Nabavite potrebne komponente koje se nalaze na priloženoj listi (postoje veze za kupnju ili pregled njihovih karakteristika). Ovo su linkovi koji paralelno uspoređuju karakteristike kao karakteristike

Nadogradite "uradi sam" lonac za zalijevanje sa WiFi -em u alarmni uređaj za otkrivanje kretnji za otkrivanje pokreta "Uradi sam": 17 koraka

Nadogradite "uradi sam" lonac za zalijevanje sa WiFi -jem u aparat za alarme za otkrivanje kretnji za otkrivanje pokreta "Uradi sam": U ovom članku pokazat ćemo vam kako nadograditi svoj lonac za samolijevanje s vlastitim WiFi -jem u DIY lonac za samolijevanje s WiFi -jem i alarmom za detekciju kretanja. niste pročitali članak o tome kako izgraditi lonac za samostalno zalijevanje s WiFi -jem, možete fin