Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:04.

- Zadnja izmjena 2025-01-23 14:37.

U ovom vodiču ćemo koristiti FPGA za upravljanje vanjskim LED krugom. Implementirat ćemo sljedeće zadatke

(A) Koristite tipke na FPGA Cyclone IV DuePrologic za upravljanje LED diodama.

(B) LED dioda blica povremeno se uključuje i isključuje

Video demo

Laboratorijski meni:

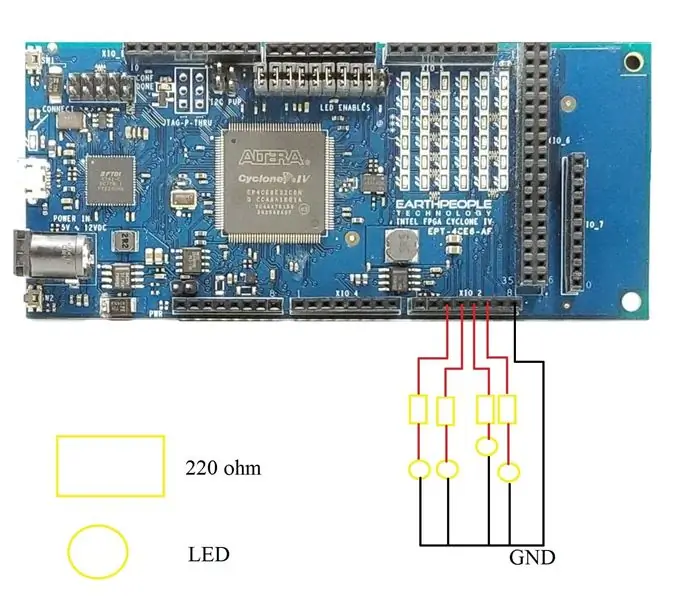

Korak 1: Izgradite elektroničko kolo

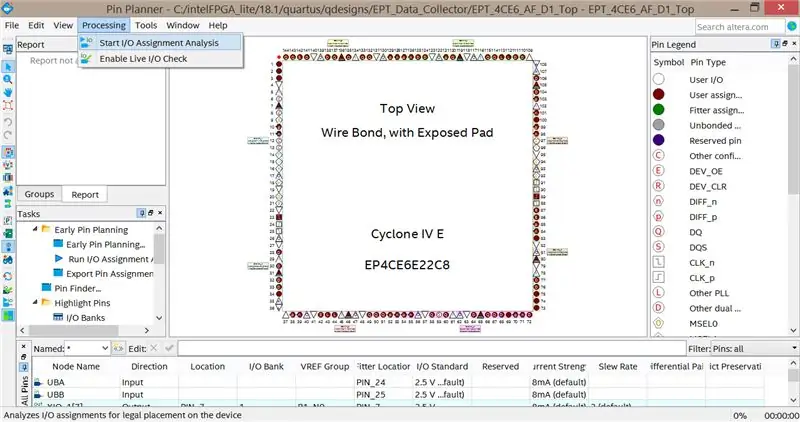

Korak 2: Provjerite Pin Planner i uredite Verilog kod

Korak 3: Uredite Verilog kôd

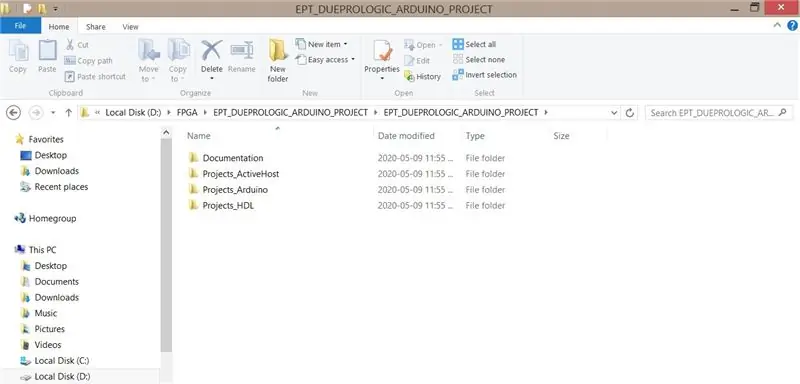

Kada kupujete FPGA DueProLogic, trebali biste dobiti DVD. Nakon što otvorite "Projects_HDL", trebali biste vidjeti originalnu datoteku koda

Dodajte označeni kôd. Registrira I/O portove i dodjeljuje brojeve portovima.

izlazna žica [7: 0] XIO_1, // XIO-D2-D9

izlazna žica [5: 0] XIO_2, // XIO-D10-D12

izlazna žica [5: 0] XIO_3, // XIO-D22-D29

ulazna žica [5: 0] XIO_4, // XIO-D30-D37

ulazna žica [5: 0] XIO_5, // XIO-D38-D45

izlazna žica [4: 0] XIO_6_OUT, // XIO-D46-D53

ulazna žica [31: 5] XIO_6, // XIO-D46-D53

izlazna žica [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

ulazna žica UBA, // Prekidači tipkama

ulazna žica UBB // Prekidači na dugme

dodijeli XIO_1 [3] = start_stop_cntrl;

dodijeli XIO_2 [1] = start_blinky; // LED blic LED uključen i isključen

dodijeli XIO_2 [2] = 1'b1; // izlaz HIGH

dodijeli XIO_2 [3] = ~ UBA; // Pritisnite dugme A

dodijeliti XIO_2 [4] = UBB; // Pritisnuti dugme B

dodijeli c_enable = XIO_5 [2];

dodijeli LEDExt = XIO_5 [5];

Zatim moramo postaviti tajmer odgode. Komentirajte izvorni kod mjerača vremena i napišite novu funkciju tajmera

//-----------------------------------------------

// LED Treperenje treperi

//-----------------------------------------------

/*

uvijek @(postavljen CLK_66 ili negedge RST)

početi

ako (! RST)

start_blinky <= 1'b0;

else

početi

if (control_register [7: 4]> 0)

start_blinky <= 1'b1;

else

start_blinky <= 1'b0;

kraj

kraj

*/

reg [31: 0] ex;

početni početak

ex <= 32'b0;

start_blinky <= 1'b0;

kraj

uvijek @(postavljeno CLK_66)

početi

ex <= ex + 1'b1;

if (ex> 100000000) // blic uključen/isključen ~ 1,6 sekundi, takt 66MHz

početi

start_blinky <=! start_blinky;

ex <= 32'b0;

kraj

kraj

//-----------------------------------------------

// Brojač odgode LED kašnjenja

//-----------------------------------------------

/*

uvijek @(postavljeni CLK_66 ili negedge RST)

početi

ako (! RST)

vodioc_zakasnelog_kašnjenja <= TIMER_LOW_LIMIT;

else

početi

ako (navedite [SELECT_MODE])

led_delay_counter <= timer_value;

inače ako (navedite [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

kraj

kraj*/

Korak 4: Sastavite Verilog kod

Pritisnite "Pokreni kompilaciju" u Quartusu, poruka o grešci ne bi trebala biti generirana.

Ako primite poruku o grešci o više pinova. Idite na Zadaci -> Uređaj -> Opcije uređaja i pinova -> Dvonamjenske pinove -> promijenite vrijednost odgovarajućeg pina u "Koristi kao običan I/O".

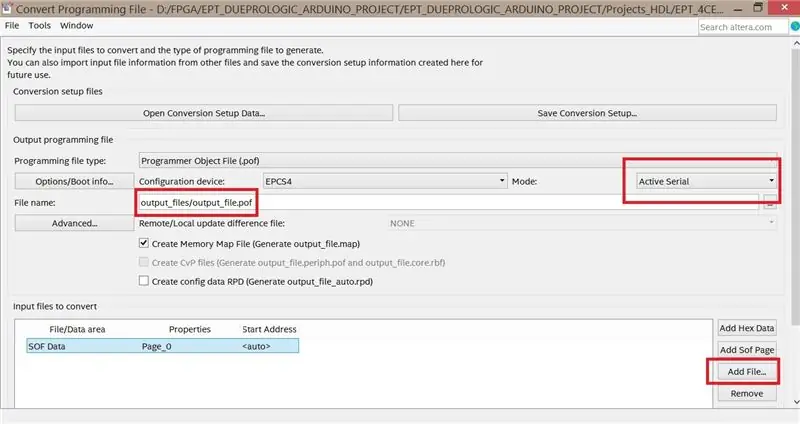

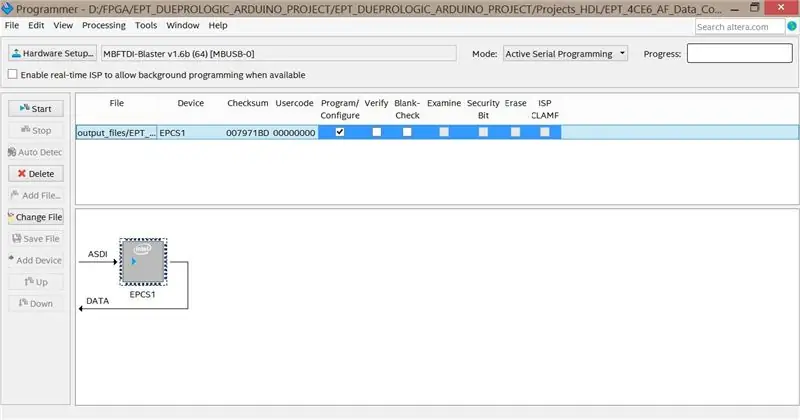

Nakon kompilacije, trebali biste izravno dobiti pof izlaznu datoteku. Ako vaš softver nije ažuriran, možda ćete dobiti samo sof datoteku. Kada se to dogodi, kliknite "Datoteka" u Quartusu -> "pretvori programske datoteke". Promijenite postavke označene crvenim okvirima.

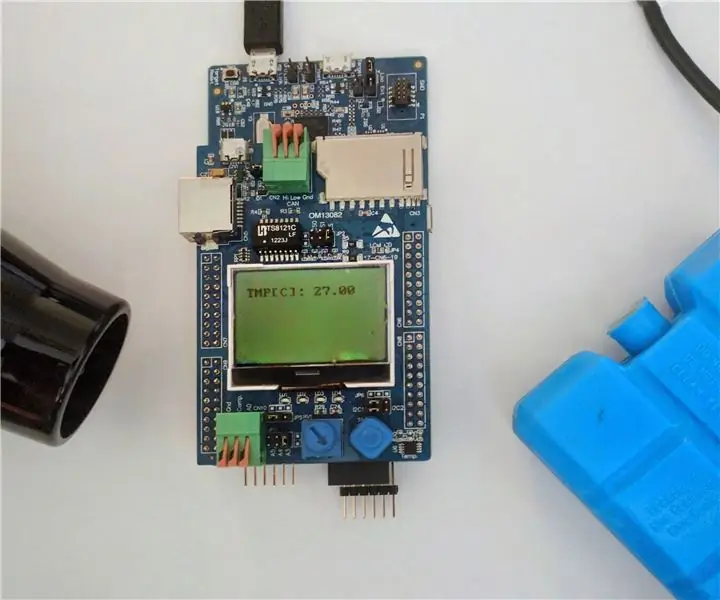

Korak 5: Pokušajmo

Na kraju krajeva, trebalo bi raditi !!! Žuta LED lampica je uvek uključena. Crvena LED lampica treperi. Plava LED dioda se isključuje ako pritisnete dugme B. Zelena LED lampica se uključuje ako pritisnete dugme A

Preporučuje se:

FPGA Cyclone IV DueProLogic kontroliše Raspberry Pi kameru: 5 koraka

FPGA Cyclone IV DueProLogic kontrolira Raspberry Pi kameru: Unatoč tome što je FPGA DueProLogic službeno dizajniran za Arduino, učinit ćemo FPGA i Raspberry Pi 4B komunikacijskim. Tri zadatka su implementirana u ovom vodiču: (A) Istovremeno pritisnite dva tastera na FPGA za okretanje ugla

FPGA Cyclone IV DueProLogic kontrole servo motor: 4 koraka

FPGA Cyclone IV DueProLogic kontrole servo motor: U ovom vodiču ćemo napisati Verilog kod za upravljanje servo motorom. Servo SG-90 proizvodi Waveshare. Kada kupite servo motor, možda ćete dobiti tehnički list koji navodi radni napon, maksimalni okretni moment i predloženi Pu

DIY VR traka za trčanje- Basys3 FPGA-Digilent takmičenje: 3 koraka

DIY VR traka za trčanje- Basys3 FPGA-Digilent takmičenje: Želite li izgraditi VR traku za trčanje na kojoj možete pokrenuti aplikacije i igre za računare? Onda ste došli na pravo mjesto! U konvencionalnim igrama koristite miš i tastaturu za interakciju s okolinom. Stoga moramo poslati

Mojo FPGA razvojni odbor Štit: 3 koraka

Štit za razvojnu ploču Mojo FPGA: Povežite svoju razvojnu ploču Mojo sa vanjskim ulazima sa ovim štitom. Šta je razvojna ploča Mojo? Mojo razvojna ploča je razvojna ploča zasnovana na Xilinx spartan 3 FPGA. Ploču proizvodi Alchitry. FPGA su vrlo korisne

Napravite bilo koji senzor od FPGA: 4 koraka

Napravite bilo koji senzor od FPGA: Većina proizvođača pokušala je barem jednom u životu izgraditi termometar, možda onaj koji imaju kod kuće nije dovoljno pametan, ili možda misle da mogu izgraditi sljedeći NEST. Ipak, u jednom trenutku imali su mikrokontroler sa svojim stanjem