Sadržaj:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:05.

- Zadnja izmjena 2025-01-23 14:37.

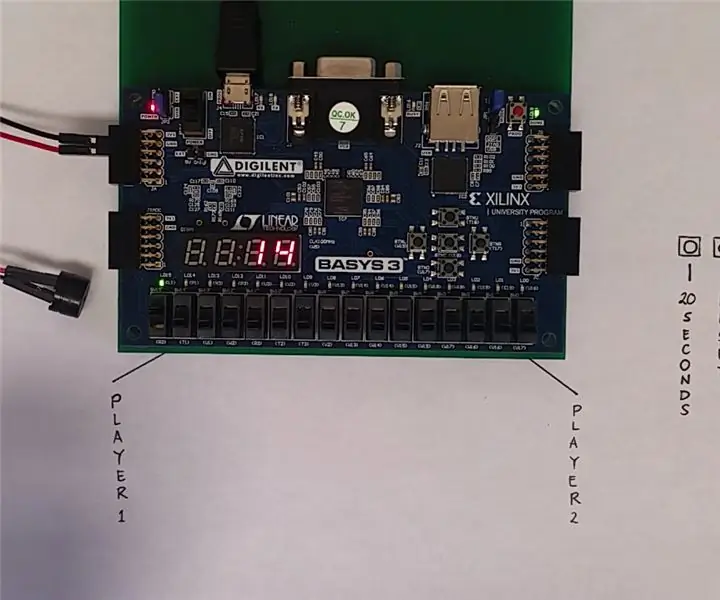

Konkurentni sistem zvučnih signala dizajniran u ovom projektu funkcioniše slično sistemima zvučnih signala koji se koriste na regionalnim i nacionalnim takmičenjima u naučnim zdjelama. Ovaj projekat je inspirisan mojim angažovanjem sa timom naučne skole moje srednje škole tokom tri godine. Oduvijek smo imali želju ponovno stvoriti zaključavanje zujalice sa tajmerom od 5 i 20 sekundi.

Da bi se dobila neka pozadina u vezi sa sistemom zujalica, zvučnici iz zdjele za nauku programirani su za unos maksimalno 8 svirača (sa 8 zasebnih zvučnika). Kada se pritisne jedan zvučni signal, zvučni signal prve osobe će zasvijetliti kako bi pokazao koji igrač prima pitanje. Ostatak igrača bit će "zaključani", što znači da njihovi zujalici neće reagirati sve dok moderator ne resetira sistem zujalica.

Nakon što moderator pročita pitanja, on će pritisnuti dugme za pokretanje odbrojavanja koje će biti prikazano na ekranu sa sedam segmenata. Nakon pitanja "toss-up", moderator može pritisnuti desno dugme za početak odbrojavanja od 5 sekundi. U međuvremenu, nakon "bonus" pitanja, moderator može pritisnuti lijevo dugme za početak odbrojavanja od 20 sekundi. Kada mjerač vremena dosegne nulu, zvučni signal će pokazati da je playeru isteklo vrijeme.

Da bi resetovao sistem i tajmer za odbrojavanje, moderator može pritisnuti centralno dugme. Da biste poništili mehanizam za zaključavanje i LED diode igrača, prekidači za igrača 1 i igrača 2 moraju biti u niskom položaju.

Korak 1: Materijali

Trebat će vam sljedeće:

- Basys3 ploča (ili ekvivalentna FPGA ploča)

- Micro-B USB kabl

- Zvučnik (koristio sam pasivni zvučnik)

- 2 žice

- Softver za implementaciju na FPGA (koristio sam Vivado)

- Sistem datoteka konkurentnog zujalica

Korak 2: Dijagram Crne kutije

Dijagram crne kutije prikazuje ulaze i izlaze koji će se koristiti u ovom sistemu zujalice.

ULAZI:

player1, player2 Ovi ulazi povezani su s dva prekidača na Basys3 ploči. Radi praktičnosti, koristit će se krajnji lijevi i krajnji desni prekidač.

reset Središnje dugme će se koristiti za predstavljanje dugmeta za resetovanje.

count_down_20_sec Lijevo dugme će se koristiti za predstavljanje tajmera od 20 sekundi.

count_down_5_sec Desno dugme će se koristiti za predstavljanje dugmeta tajmera od 20 sekundi. Da biste osigurali da se i tajmer od 20 i 5 sekundi pokreće, držite pritisnuto dugme dok sedmosegmentni ekran ne prikaže tajmer.

CLK FPGA ploča će generirati sat koji radi s frekvencijom od 10 ns.

REZULTATI:

zvučnik Izlaz zvučnika je spojen na vanjski zujalicu ili zvučnik. Zvučnik ćete morati spojiti na JAS pmod priključke Basys3 ploče. Ovaj korak će biti opisan u nastavku.

speaker_LED Ovaj izlaz je povezan sa LED -om na sredini ploče i samo će pokazati kada je izlaz zvučnika na FPGA -u visok. Ovo možete koristiti za testiranje vanjskog zvučnika. Imajte na umu da neki od pmod priključaka možda neće dobro funkcionirati, pa možete isprobati različite i pomoću LED -a provjeriti treba li zvučnik biti uključen.

SEGMENTI Ovaj izlaz je povezan sa osam pojedinačnih segmenata na sedmo-segmentnom ekranu, uključujući decimalnu tačku.

DISP_EN Ovaj izlaz je spojen na četiri anode na ekranu sa sedam segmenata.

player_LED Ovaj izlaz je 2-snopni signal koji je spojen na LED diode iznad prekidača player1 i player2. Prvi igrač koji okrene odgovarajući prekidač bit će označen LED diodom. Imajte na umu da obje LED diode ne mogu biti uključene istovremeno.

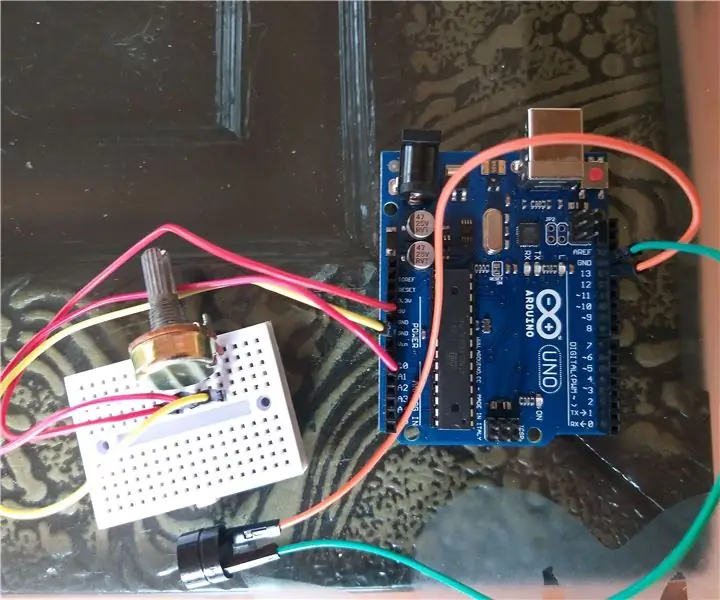

Korak 3: Povezivanje vanjskog zvučnika

Da biste spojili vanjski zvučnik na Basys3 ploču, uzmite svoje dvije žice i spojite ih kako je prikazano na gornjoj slici. Bijela linija povezuje negativni terminal zvučnika s uzemljenjem na ploči. Crvena linija povezuje pozitivni terminal zvučnika s pAm portom JA10 na ploči.

Datoteka ograničenja je dizajnirana tako da svaki port od JA1 do JA10 treba raditi. Međutim, neki pinovi na ploči ne reagiraju, pa ako JA10 ne radi, možete isprobati druge portove.

Korak 4: Strukturni dijagram

Gornja slika prikazuje strukturni dijagram konkurentnog sistema zujalica, uključujući sve komponente koje čine glavni modul. Njihovi opisi su sljedeći:

player_lockout_LED1 LED komponenta zaključavanja playera je stroj sa konačnim stanjem koji koristi jednokratno kodiranje. Ima četiri ulaza: player1, player2, reset i CLK. Sadrži 2-bitni paket izlaza player_LED. Ulazi i izlazi komponente player_lockout_LED1 svi su izravno povezani s identično imenovanim ulazima i izlazima glavnog modula.

buzzer_tone1 Komponenta zujalice je zasnovana na ovom kodu objavljenom na forumu

stackoverflow.com/questions/22767256/vhdl-… Međutim, on je modifikovan tako da emituje kontinuirani zvuk sa frekvencijom od 440 Hz (Napomena). Ulaz za omogućavanje povezan je sa signalom koji omogućava zujalicu koji je izlaz komponente down_counter_FSM1.

clk_div1 Komponenta razdjelnika sata je izmijenjena verzija satnog razdjelnika profesora Bryana Mealyja na PolyLearnu. Usporava sat pa je izlazni period 1 sekunda.

down_counter_FSM1 Brojač dolje je FSM dizajniran za odbrojavanje do nule. Dva moguća vremena početka su 20 ili 5 koje bira korisnički unos. On emitira '1' kada je mjerač vremena dosegao nulu, što znači da je vrijeme isteklo. Ovaj izlaz djeluje kao omogućavanje komponente tona zujalice. Brojač također emitira 8-bitni paketni signal koji šalje 8-bitni BCD koji se šalje segmentnom dekoderu. Drugi izlaz je counter_on koji je također spojen na važeći ulaz na segmentnom dekoderu.

sseg_dec1 Sedmosegmentna komponenta dekodera dostupna je na PolyLearnu, a napisao ju je profesor Bryan Mealy. Koristi BCD ulaz koji pruža down_counter_FSM1, i emituje decimalni ekvivalent na sedmosegmentnom ekranu. Kada je brojač uključen, tada je važeći ulaz visok. Ovo omogućava dekoderu da prikaže decimalni broj na sedmosegmentnom ekranu. Kada je brojač isključen, tada je važeći ulaz nizak. Ekran sa sedam segmenata tada će prikazati samo četiri crtice.

Korak 5: Dijagram konačnih mašina (FSM)

Lista osjetljivosti za stroj konačnih stanja uključuje player1, player2, reset i sat. Izlaz FSM-a je 2-bitni paket player_LED spojen na dvije LED diode na Basys3 ploči. Mašina konačnih stanja prikazuje sljedeća tri stanja:

ST0 je stanje početka. U tom stanju, dvije LED diode su isključene. FSM će ostati u ovom stanju ako su i igrač1 i igrač2 niski. Asinhroni reset također postavlja stanje na ST0. Kada je prekidač player1 postavljen na visoko, sljedeće stanje će biti ST1. Ako je prekidač player2 postavljen na visoko, sljedeće stanje će biti ST2.

ST1 je stanje za koje svijetli LED lampica player1. FSM će ostati u ovom stanju za svaki ulaz. To znači da će čak i kada je prekidač player2 postavljen na visoko odmah nakon što je prekidač player1 visok, on će ostati u ST1. Samo asinhroni reset može postaviti sljedeće stanje na ST0.

ST2 je stanje za koje je uključena LED lampica player2. Slično ST !, FSM će ostati u ovom stanju za bilo koji ulaz, čak i kada je prekidač player1 postavljen na visoko odmah nakon što je prekidač player2 visok. Opet, samo asinhroni reset može postaviti sljedeće stanje na ST0.

Preporučuje se:

Kako koristiti PIR senzor i modul zujalice - Vodič za Visuino: 6 koraka

Kako koristiti PIR senzor i modul zujalice - Vodič za Visuino: U ovom ćemo vodiču naučiti kako koristiti PIR senzor i modul zujalice za stvaranje zvuka svaki put kada PIR senzor detektira pokret. Pogledajte demonstracijski video

Super Mario pomoću zujalice: 3 koraka

Super Mario pomoću zujalice: Slušanje muzike opušta naš um i dušu. Omogućimo dodavanje muzike vašim arduino projektima koristeći jednu komponentu, zujalicu. Ovaj sjajan projekt pronašao sam koristeći Buzzer koji svira super mario pjesmu koju je napisao Dipto Pratyaksa na instrukcijama. Pored toga

Jednostavna muzika zujalice: 6 koraka

Jednostavna muzika zujalice: Jednostavna biblioteka za izlaz vlastitih pjesama s Arduinom putem zujalice ili zvučnika. Mali primjer pjesme "que; praeludium" by Johann Sebastian Bach

Upravljajte zvukom zujalice pomoću Arduina: 7 koraka

Upravljajte zvukom zujalice pomoću Arduina: Postoje mnogi interaktivni radovi koji se mogu dovršiti s Arduinom, najčešći i najčešće korišteni je prikaz zvuka i svjetla. Najčešće komponente koje mogu stvarati zvuk su zujalica i truba. Uporedite to dvoje, zujalica je jednostavnija

Moj pokušaj melodije zujalice dugmeta Arduino: 11 koraka

Moj pokušaj melodije zujalice dugmeta Arduino: U ovom vodiču ću vam pokazati kako dugme može pokrenuti melodiju. Tokom školske godine mnoge naše živote vode zvona ili tonovi koji nam daju do znanja kada je vrijeme za polazak ili vrijeme za polazak. Većina nas rijetko zastaje i razmišlja o tome kako se razlikuju